# Assignment of bachelor's thesis

Title: Exploiting Logic Synthesis in SAT-solving

Student: Jan Kimr

**Supervisor:** doc. Ing. Petr Fišer, Ph.D.

Study program: Informatics

Branch / specialization: Artificial Intelligence 2021

**Department:** Department of Applied Mathematics

Validity: until the end of summer semester 2024/2025

#### Instructions

This work aims to explore the influence of logic synthesis on SAT solving. This is, to experimentally find out what simplifications (transformations) of logic expressions (CNF) lead to a SAT solver speed-up. Both positive and negative influences are reported in literature. However, no thorough exploration has been done yet.

Particular goals of the Thesis are:

- Apply different logic synthesis techniques to different SAT problem instances.

- Perform respective experiments and determine for what types of instances the optimization reduces the overall SAT-solving time and which optimization process is the most efficient.

- Perform the experiments using several available (open-source) SAT solvers and compare the results.

- In the case of positive findings (i.e., the pre-optimization reduces the overall run time), use the obtained knowledge to optimize some existing algorithms repeatedly calling the SAT-solver (e.g., SAT-based ATPG).

Bachelor's thesis

# EXPLOITING LOGIC SYNTHESIS IN SAT-SOLVING

Jan Kimr

Faculty of Information Technology Department of Applied Mathematics Supervisor: doc. Ing. Petr Fišer, Ph.D. May 14, 2024

Czech Technical University in Prague Faculty of Information Technology © 2024 Jan Kimr. All rights reserved.

This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

Citation of this thesis: Kimr Jan. Exploiting Logic Synthesis in SAT-solving. Bachelor's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2024.

# Contents

| A  | cknov | wledgn        | nents                                                              | vi   |

|----|-------|---------------|--------------------------------------------------------------------|------|

| D  | eclar | ation         |                                                                    | vii  |

| A  | bstra | $\mathbf{ct}$ |                                                                    | viii |

| Li | st of | abbre         | viations                                                           | ix   |

| In |       | uction        |                                                                    | 1    |

|    | Obje  | ectives       |                                                                    | 1    |

| 1  | The   | eorv          |                                                                    | 3    |

|    | 1.1   |               | an Satisfiability Problem (SAT)                                    |      |

|    |       | 1.1.1         | Tseitin transformation                                             |      |

|    |       | 1.1.2         | Encoding problems and practical use of SAT                         | 6    |

|    | 1.2   | SAT s         | solving algorithms                                                 |      |

|    |       | 1.2.1         | DPLL algorithm                                                     |      |

|    |       | 1.2.2         | Conflict-driven clause learning (CDCL)                             |      |

|    | 1.3   | Solver        | s used in the experimental part                                    | 8    |

|    |       | 1.3.1         | zChaff                                                             |      |

|    |       | 1.3.2         | MiniSat                                                            | 9    |

|    |       | 1.3.3         | Glucose                                                            | 9    |

|    | 1.4   | Logic         | synthesis                                                          | 10   |

|    | 1.5   | Optim         | num circuit generation                                             | 10   |

|    | 1.6   | Auton         | natic Test Pattern Generation (ATPG)                               | 10   |

|    | 1.7   | Machi         | ne learning models and related topics used in evaluating practical |      |

|    |       | use of        | synthesis                                                          | 11   |

|    |       | 1.7.1         | Model training and evaluation                                      | 11   |

|    |       | 1.7.2         | Linear regression                                                  | 12   |

|    |       | 1.7.3         | Logistic regression                                                | 12   |

|    |       | 1.7.4         | Naive Bayes                                                        | 12   |

|    |       | 1.7.5         | K-nearest neighbours                                               | 12   |

|    |       | 1.7.6         | Decision tree                                                      | 13   |

|    |       | 1.7.7         | Random forest                                                      | 13   |

|    |       | 1.7.8         | Gradient boosting decision trees                                   | 13   |

|    |       | 1.7.9         | Data preprocessing (feature normalization)                         |      |

|    | 1.8   | Usage         | of logic synthesis in SAT-solving                                  | 14   |

Contents

| <b>2</b> | $\mathbf{E}\mathbf{x}\mathbf{p}$ | erimei   | nts                                       | 15   |

|----------|----------------------------------|----------|-------------------------------------------|------|

|          | 2.1                              | Experi   | imental Setup                             | . 15 |

|          | 2.2                              | SATL     | IB benchmark instances                    | . 16 |

|          |                                  | 2.2.1    | Synthesis influence on CNF properties     | . 16 |

|          |                                  | 2.2.2    | Synthesis influence on solving time       | . 17 |

|          | 2.3                              | MinCi    | rc instances                              | 26   |

|          |                                  | 2.3.1    | Synthesis influence on CNF properties     | . 26 |

|          |                                  | 2.3.2    | Synthesis influence on solving time       |      |

|          | 2.4                              | ATPG     | finstances                                |      |

|          |                                  | 2.4.1    | Synthesis influences on solving time      | 35   |

| 3        | Usi                              | ng syn   | thesis in SAT-solving                     | 38   |

|          | 3.1                              | Explor   | red approaches                            | . 38 |

|          |                                  | 3.1.1    | Restarting                                | . 38 |

|          |                                  | 3.1.2    | Selecting instances to run with synhtesis | . 38 |

|          |                                  | 3.1.3    | Selecting instances for restarting        | . 39 |

|          | 3.2                              | Model    | training and evaluation                   | . 39 |

|          | 3.3                              | MinCi    | rc instances                              | 40   |

|          |                                  | 3.3.1    | Data                                      | 40   |

|          |                                  | 3.3.2    | Results                                   | 41   |

|          | 3.4                              | ATPG     | f instances                               | 41   |

|          |                                  | 3.4.1    | Data                                      | 42   |

|          |                                  | 3.4.2    | Results                                   | 42   |

| 4        | Disc                             | cussion  | 1                                         | 45   |

| 5        | Cor                              | nclusio  | n                                         | 47   |

| C        | oncei                            | nts of t | the attachment                            | 53   |

# List of Figures

| 1.1  | Example of decision tree for binary classification                                                                                                | 13 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      |                                                                                                                                                   |    |

|      | List of Tabl                                                                                                                                      | es |

|      |                                                                                                                                                   |    |

| 2.1  | SATLIB benchmark: influence of logic synthesis on number of variables .                                                                           | 17 |

| 2.2  | SATLIB benchmark: influence of logic synthesis on number of clauses                                                                               | 18 |

| 2.3  | SATLIB benchmark: influence of logic synthesis on clause-variable ratio .                                                                         | 18 |

| 2.4  | SATLIB benchmark: numbers of unsatisfiable instances which were trans-                                                                            |    |

|      | formed by synthesis into trivial ones (i.e., for variable $a$ , the CNF would                                                                     |    |

|      | be $a \wedge \neg a$ )                                                                                                                            | 19 |

| 2.5  | SATLIB benchmarks: separated by slashes are numbers of instances (1)                                                                              |    |

|      | which were solved in 2000 seconds (real-time) both with and without                                                                               |    |

|      | synthesis, (2) which were solved in 2000 seconds (real-time) with synthesis                                                                       |    |

|      | but not without it, (3) which were solved in 2000 seconds (real-time)                                                                             |    |

|      | without synthesis but not with it, (4) which were solved in 2000 seconds (real-time) neither with nor without synthesis. In case values (2), (3), |    |

|      | and (4) are all zeroes, they are omitted                                                                                                          | 22 |

| 2.6  | SATLIB benchmarks: ratio of instances whose time of solving decreased                                                                             | 22 |

| 2.0  | after using synthesis preprocessing. Instances that were solved neither                                                                           |    |

|      | with nor without synthesis are left out                                                                                                           | 23 |

| 2.7  | SATLIB benchmarks: potential influence of synthesis on solving time (i.e.,                                                                        |    |

|      | using synthesis only when decreases solving time of an instance). Only                                                                            |    |

|      | instances solved both with and without synthesis are considered. The                                                                              |    |

|      | average time is calculated from instances solved without synthesis within                                                                         |    |

|      | the time limit.                                                                                                                                   | 24 |

| 2.8  | SATLIB benchmarks: influence of synthesis on solving time if used always;                                                                         |    |

|      | values larger than or equal to $+1000\%$ are replaced by "-". Only instances                                                                      |    |

|      | solved both with and without synthesis are considered. The average time                                                                           |    |

| 2.0  | is calculated from instances solved without synthesis within the time limit.                                                                      | 25 |

| 2.9  | MinCirc: influence of logic synthesis on number of variables                                                                                      | 27 |

| 2.10 | g •                                                                                                                                               | 27 |

| 2.11 | MinCirc: influence of logic synthesis on clause-variable ratio                                                                                    | 28 |

| 2.12 | MinCirc: numbers of unsatisfiable instances which were transformed by                       |                |

|------|---------------------------------------------------------------------------------------------|----------------|

|      | synthesis into trivial ones (i.e., for variable $a$ , the CNF would be $a \wedge \neg a$ ). | 28             |

| 2.13 | MinCirc: separated by slashes are numbers of instances (1) which were                       |                |

|      | solved in 2000 seconds (real-time) both with and without synthesis, (2)                     |                |

|      | which were solved in 2000 seconds (real-time) with synthesis but not with-                  |                |

|      | out it, (3) which were solved in 2000 seconds (real-time) without synthesis                 |                |

|      | but not with it, (4) which were solved in 2000 seconds (real-time) neither                  |                |

|      | with nor without synthesis. In case values (2), (3), and (4) are all zeroes,                |                |

|      | they are omitted                                                                            | 31             |

| 2.14 | MinCirc: ratio of instances whose time of solving decreased after using                     |                |

|      | synthesis preprocessing. Instances that were solved neither with nor with-                  |                |

|      | out synthesis are left out.                                                                 | 32             |

| 2.15 | MinCirc: potential influence of synthesis on solving time (i.e., using syn-                 |                |

|      | thesis only when decreases solving time of an instance). Only instances                     |                |

|      | solved both with and without synthesis are considered. The average time                     |                |

|      | is calculated from instances solved without synthesis within the time limit.                | 33             |

| 2.16 | MinCirc: influence of synthesis on solving time if used always; values                      |                |

|      | larger than or equal to $+1000\%$ are replaced by "-". Only instances solved                |                |

|      | both with and without synthesis are considered. The average time is                         |                |

|      | calculated from instances solved without synthesis within the time limit.                   | 34             |

| 9 17 | ATPG circuits: ratio of circuits whose time of solving decreased after                      | 94             |

| 2.11 |                                                                                             | 36             |

| 0.10 | using logic synthesis                                                                       | 50             |

| 2.18 | ATPG circuits: potential influence of synthesis on solving time (i.e., using                | 0.0            |

| 0.10 | synthesis only when decreases solving time of an instance)                                  | 36             |

| 2.19 | ATPG circuits: influence of synthesis on solving time if used always                        | 37             |

| 3.1  | Practical use of synthesis: results of ten best models by a decrease in                     |                |

| 0.1  | solving time on MinCirc instances using the MINISAT solver with st synthesis                | 19             |

| 3.2  |                                                                                             | 42             |

| ე.∠  | Practical use of synthesis: results of ten best models by a decrease in                     |                |

|      | solving time on MinCirc instances using the MINISAT solver with 6-LUT-                      | 40             |

| 0.0  | 1x synthesis                                                                                | 42             |

| 3.3  | Practical use of synthesis: results of ten best models by a decrease in                     | 4.4            |

| a .  | solving time on ATPG instances with st synthesis                                            | 44             |

| 3.4  | Practical use of synthesis: results of ten best models by a decrease in                     |                |

|      | solving time on ATPG instances with $st$ - $re2$ - $1x$ synthesis                           | 44             |

|      |                                                                                             |                |

|      |                                                                                             |                |

|      |                                                                                             |                |

|      |                                                                                             |                |

|      | List of code listin                                                                         | ന്ട            |

|      | List of code listin                                                                         | 8 <sup>5</sup> |

|      |                                                                                             |                |

| 1 1  | DDI I - l:4h [16]                                                                           | 7              |

| 1.1  | DPLL algorithm pseudocode [16]                                                              | 7              |

I would like to thank my supervisor, doc. Ing. Petr Fišer, Ph.D., for all the help and valuable comments he provided me during the writing of this thesis.

#### Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular that the Czech Technical University in Prague has the right to conclude a license agreement on the utilization of this thesis as a school work under the provisions of Article 60 (1) of the Act.

In Prague on May 14, 2024

#### **Abstract**

This thesis analyzes the possibility of using logic synthesis and optimization to speed up solving satisfiability problem (SAT) instances coming from both the standard benchmarks and different practical applications.

Logic optimization, in principle, influences an instance in two main ways: (1) it reduces its size, and (2) structures making the instance difficult to solve could be dissolved. However, it is necessary to consider both times of synthesis and solving, as speed up in solving achieved by "stronger" synthesis could be outweighed by synthesis time, leading to an overall time increase.

The efficiency of logic synthesis and optimization was evaluated using different instances and syntheses. It can both positively and negatively influence the overall time of solving, which mostly depends on the instance size and used synthesis. Based on the results, recommendations regarding the practical use of synthesis are made.

**Keywords** SAT, Boolean satisfiability, logic synthesis, logic optimization, optimum circuit generation, ATPG

#### Abstrakt

Tato práce se zabývá možností využití logické syntézy a optimalizace ke zrychlení řešení instancí problému splnitelnosti (SAT) pocházejících ze standardních benchmarků i praktických aplikací.

Logická syntéza může v principu ovlivnit instanci dvěma způsoby: (1) zmenšením velikosti a (2) rozptýlením struktur, které komplikovaly řešení původní instance. Nicméně při použití syntézy je nutné vzít v potaz nejen čas řešení upravené instance, ale i čas syntézy. Může se stát, že zrychlení dosažené při řešení SATu bude převáženo časem syntézy samotné.

Efektivita logické syntézy a optimalizace byla vyhodnocena na různých instancích a s různými syntézami. Syntéza ovlivňuje celkový čas řešení pozitivně i negativně v závislosti zejména na velikosti instance a použité syntéze. Na základě naměřených výsledků jsou popsány možnosti praktického využití syntézy.

**Klíčová slova** SAT, splnitelnost Boolovských fromulí, logická syntéza, logická optimalizace, generování optimálních obvodů

#### List of abbreviations

- AI Artificial Intelligence

- AIG AND-inverter-graph

- ATPG Automatic Test Pattern Generation

- BLIF Berkeley Logic Interchange Format

- CDCL Conflict-Driven Clause Learning

- CNF Conjunctive Normal Form

- CPU Central Processing Unit

- CV Cross-validation

- DAG Directed Acyclic Graph

- DIMACS Center for Discrete Mathematics and Theoretical Computer Science

- DPLL or DLL Davis-(Putnam)-Logemann-Loveland algorithm

- EDA Electronic Design Automation

- FPGA Field Programmable Gate Arrays

- HDL Hardware Description Language

- LBD Literal Block Distance

- LUT LookUp Table

- ML Machine Learning

- NB Naive Bayes

- PI Primary Input

- SAT Boolean Satisfiability Problem

- SMT Satisfiability Modulo Theories

- VSIDS Variable State Independent Decaying Sum

# Introduction

The Boolean satisfiability problem (SAT) involves determining whether some variable valuation satisfies a given formula and, if so, finding such valuation. Although this problem is NP-complete, fast and efficient SAT solvers have been developed in the last two decades. This development has made it possible to use these solvers in practical areas such as artificial intelligence or circuit design.

Specifically, in circuit design, many Electronic Design Automation (EDA) tools use SAT or its derivatives, like pseudo-Boolean optimization or Satisfiability modulo theories (SMT). Furthermore, SAT is used for model-checking engines and the Automated Test Pattern Generation process (ATPG). Even though SAT solvers should be efficient enough to solve instances reasonably fast, large and difficult-to-solve instances still occur in areas such as optimum circuit generation or ATPG.

The SAT instances are most commonly represented in a Conjunctive Normal Form (CNF), which can be preprocessed and optimized by logic optimization tools, hoping that the resulting SAT problem will be solved faster. Nevertheless, both time of optimization and SAT-solving must be considered; thus, finding the optimal trade-off for minimizing the run time is necessary.

This approach is not new; multiple studies dealing with the application of logic synthesis in the SAT-solving process have been published [1, 2]. However, there is no definite conclusion, as the sets of tested instances were rather limited.

This thesis focuses on experimentally evaluating three case studies in which logic optimization could speed up SAT-solving. Based on the obtained results, we attempt to make a conclusive recommendation for using (or not using) logic optimization in the SAT-solving process.

# Objectives

The primary goals of this thesis are the following:

- Apply different logic synthesis techniques to different SAT problem instances.

- Perform respective experiments and determine for what types of instances the optimization reduces the overall SAT-solving time and which optimization process is the most efficient.

Objectives 2

■ Perform the experiments using several available (open-source) SAT solvers and compare the results.

■ In the case of positive findings (i.e., the pre-optimization reduces the overall run time), use the obtained knowledge to optimize some existing algorithms repeatedly calling the SAT-solver (e.g., SAT-based ATPG).

## Chapter 1

# Theory

In this chapter, topics and concepts used in Chapters 2 and 3 are introduced. We start by defining the SAT problem and describing its usefulness, followed by a brief description of algorithms for solving it. Specifics of three different implementations of these algorithms – SAT solvers used in the following chapters are then provided.

Logic synthesis can be used to preprocess SAT instances before solving them. It is briefly explained what it is and how it can be used specifically for SAT instance preprocessing.

Two algorithms, where the SAT is frequently used, are presented to give an idea of practical problems where it can be used and how the particular SAT instances are created. These are optimum circuit generation and (SAT-based) ATPG. The influence of logic synthesis on instances created while solving these problems is evaluated in the following chapters.

In most cases, logic synthesis speeds up the solving of only a small number of SAT instances (around 10–30%). One of the approaches to utilize it, despite the low rate of improved instances, is to find a method of selecting instances that should be preprocessed using synthesis to speed up as many instances as possible while not slowing down others. For this purpose, machine learning models are used. An overview of different models, as well as other aspects of machine learning, is provided.

Since the approach of using synthesis to speed up SAT-solving is not novel, the results of two papers on this topic are shortly discussed.

# 1.1 Boolean Satisfiability Problem (SAT)

. . . . . . . . . . . .

A Boolean formula consists of variables that can be assigned a logic value, either 0 or 1, logical connectives  $(\neg, \land, \lor)$ , and parentheses determining the priority of operations. There are other logical connectives than the presented ones (i.e.,  $\implies$ ,  $\iff$ ); nevertheless, each formula can be rewritten to one using just  $\neg$ ,  $\land$ , and  $\lor$ . When all variables are assigned values, the formula evaluates to either 0 or 1.

The SAT is a problem of determining whether, for a given Boolean formula, there is such variable assignment that evaluates the formula to 1 (i.e., the formula is satisfiable) or no such assignment exists (i.e., the formula is unsatisfiable). For a satisfiable formula,

one of the satisfying variable valuations is usually reported.

The SAT problem was the first one to be proven to be NP-complete [3]. As a result (unless P=NP), SAT solving has the worst-case exponential time complexity, as for n variables; there are  $2^n$  possible truth assignments to be checked. On the other hand, checking whether some variable valuation satisfies the formula can be done in polynomial time. In practice, however, instances are usually far from the worst-case, and solvers can solve large instances with many variables and clauses [4].

Each Boolean formula can be written in the conjunctive normal form (CNF), sometimes called the Product of Sums form. A literal is a variable or its negation; a clause is a literal or disjunction of multiple literals; and a formula is in CNF if it is a clause or conjunction of multiple clauses. A useful property of CNF is that in order for the formula to be satisfied, all clauses must be satisfied; conversely, if one clause is not satisfied, the whole formula can not be satisfied. An unsatisfied clause is called a conflicting clause.

There are usually many functionally equivalent CNF representations of a formula. Equation 1.1 shows an example Boolean formula in CNF. This formula has multiple satisfying assignments, one of them being a = 0, b = 1, and c = 1.

$$(\neg a \lor b \lor c) \land (\neg a \lor c) \land (b \lor \neg c) \tag{1.1}$$

There are many solvers for the SAT problem (e.g., [4, 5, 6]), which can be divided into two main groups, incomplete and complete. An incomplete solver is not guaranteed to return an answer – it has some resource limit and either finds a solution or reports a failure. These solvers usually specialize in finding valid solution while not attempting to prove the formula unsatisfiable. Incomplete solvers are usually significantly faster compared to complete solvers which will always find a solution or prove unsatisfiability [7].

Most solvers accept formulas written in CNF, usually in DIMACS format [8]. The use of CNF is not limiting, as transforming a formula to CNF can be done in polynomial time using the Tseitin transformation [9].

#### 1.1.1 Tseitin transformation

Using naively de Morgan laws to transform a given Boolean formula to CNF can lead to an exponential blowup in the worst case. Fortunately, using the Tseitin transformation [9], we can get an equisatisfiable (i.e., satisfiable iff the original formula is satisfiable) formula in CNF of any Boolean formula. The resulting formula's size is linear in the original formula's size and can be found in polynomial time.

We can show the steps of the transformation on the formula F.

$$F := (a \land b) \implies \neg(c \lor \neg d) \tag{1.2}$$

We introduce a new auxiliary variable for each subformula (everything more than just a simple variable) and for the whole formula. We start with the simplest subformulas and use previously created auxiliary variables to ensure that each variable is assigned only a negation of another variable or a formula consisting of two variables joined by a binary operation.

$$x_1 := a \wedge b$$

$$x_2 := \neg d$$

$$x_3 := c \vee x_2$$

$$x_4 := \neg x_3$$

$$x_5 := x_1 \implies x_4$$

Then we put each auxiliary variable into equivalence with its formula, forming its characteristic function.

$$x_1 \iff (a \land b)$$

$$x_2 \iff \neg d$$

$$x_3 \iff (c \lor x_2)$$

$$x_4 \iff \neg x_3$$

$$x_5 \iff (x_1 \implies x_4)$$

We continue by modifying these equivalences (characteristic functions) using Boolean rules until they are in CNF. Since there is a finite number of binary operations, it is possible to prepare the CNF for each operation beforehand and then just swap the variables for the actual ones.

$$x_{1} \iff (a \land b) \equiv (x_{1} \implies (a \land b)) \land ((a \land b) \implies x_{1})$$

$$\equiv (\neg x_{1} \lor (a \land b)) \land (\neg a \lor \neg b \lor x_{1})$$

$$\equiv (\neg x_{1} \lor a) \land (\neg x_{1} \lor b) \land (\neg a \lor \neg b \lor x_{1})$$

$$x_{2} \iff \neg d \equiv (x_{2} \implies \neg d) \land (\neg d \implies x_{2})$$

$$\equiv (\neg x_{2} \lor \neg d) \land (d \lor x_{2})$$

$$x_{3} \iff (c \lor x_{2}) \equiv (x_{3} \implies (c \lor x_{2})) \land ((c \lor x_{2}) \implies x_{3})$$

$$\equiv (\neg x_{3} \lor c \lor x_{2}) \land ((\neg c \land \neg x_{2}) \lor x_{3})$$

$$\equiv (\neg x_{3} \lor c \lor x_{2}) \land (\neg c \lor x_{3}) \land (\neg x_{2} \lor x_{3})$$

$$x_{4} \iff \neg x_{3} \equiv (x_{4} \implies \neg x_{3}) \land (\neg x_{3} \implies x_{4})$$

$$\equiv (\neg x_{4} \lor \neg x_{3}) \land (x_{3} \lor x_{4})$$

$$x_{5} \iff (x_{1} \implies x_{4}) \equiv (x_{5} \implies (x_{1} \implies x_{4})) \land ((x_{1} \implies x_{4}) \implies x_{5})$$

$$\equiv (\neg x_{5} \lor \neg x_{1} \lor x_{4}) \land ((x_{1} \land \neg x_{3}) \lor x_{5})$$

$$\equiv (\neg x_{5} \lor \neg x_{1} \lor x_{4}) \land (x_{1} \lor x_{5}) \land (\neg x_{4} \lor x_{5})$$

As all the characteristic functions must be satisfied, they are concatenated by conjunction, forming the resulting formula  $F_T$  in CNF.

$$F_T := x_5 \land (\neg x_1 \lor a) \land (\neg x_1 \lor b) \land (\neg a \lor \neg b \lor x_1) \land (\neg x_2 \lor \neg d) \land (d \lor x_2) \land (\neg x_3 \lor c \lor x_2) \land (\neg c \lor x_3) \land (\neg x_2 \lor x_3) \land (\neg x_4 \lor \neg x_3) \land (x_3 \lor x_4) \land (\neg x_5 \lor \neg x_1 \lor x_4) \land (x_1 \lor x_5) \land (\neg x_4 \lor x_5)$$

$F_T$  is not equivalent to the original formula F. It is only equisatisfiable. Nevertheless, if we have a variable assignment satisfying  $F_T$ , by dropping auxiliary variables, we get a variable assignment that satisfies the original formula F [10].

#### 1.1.2 Encoding problems and practical use of SAT

Instances of many problems can be encoded in CNF and solved using a SAT solver. This can be beneficial since SAT solvers are fast, continuously developed, and optimized. Nevertheless, there are usually more strategies for encoding instances of a chosen problem, with encoding techniques having a significant impact on the efficiency of the solver [11].

We can use a simple problem called the Pigeon-hole problem to demonstrate encoding in CNF. This problem involves placing n+1 pigeons in n holes with, at most, one pigeon in each hole [12]. This obviously is not possible, but it shows how a simple problem can be transformed into the SAT.

For each pigeon i and each hole j, we create variable  $x_{i,j}$ , which is true if pigeon i is placed in hole j. For each of n+1 pigeons, we create a clause that ensures that each pigeon is placed in some hole, i.e.,  $\forall i \in \{1,\ldots,n+1\}: \bigvee_{j=1}^n x_{i,j}$ . Then, for each hole j, we create a set of clauses allowing at most one pigeon to be present, i.e.,  $\forall j \in \{1,\ldots,n\}; \forall i_1,i_2 \in \{1,\ldots,n+1\}, i_1 \neq i_2 : \neg x_{i_1,j} \vee \neg x_{i_2,j}$ . In the end, we have  $n \cdot (n+1)$  variables and  $(n+1) + n \cdot \frac{n \cdot (n+1)}{2}$  clauses [12].

The development of efficient SAT solvers led to widespread use of SAT in many areas and problem domains: "Examples include model-checking of finite-state systems, design debugging, AI planning, and haplotype inference in bioinformatics. Additional successful examples of practical applications of SAT include knowledge-compilation, software model checking, software testing, package management in software distributions, checking of pedigree consistency, test-pattern generation in digital systems, design debugging and diagnosis, identification of functional dependencies in Boolean functions, technology-mapping in logic synthesis, circuit delay computation, as well as the ones mentioned above. However, this list is incomplete as the number of applications of SAT has been on the rise in recent years." [13]

# 1.2 SAT solving algorithms

In this section, two main complete SAT-solving algorithms are described. The first one, DPLL, is not that fast and memory efficient on its own; however, it can be extended by clause learning and backjumping (CDCL), which is described the second part of this section. Many modern solvers use a combination of these two algorithms.

## 1.2.1 DPLL algorithm

In 1960, Davis and Putnam published a two-part algorithm for predicate logic theorem proving [14]. In the first part, a growing CNF formula is generated, while the second tests the formula's satisfiability. Two years later, the second part was improved by Davis, Logemann, and Loveland in [15]. In the improved version, while testing satisfiability, the formula is split into multiple parts, which are then evaluated separately as it significantly improves memory efficiency.

From this, a recursive algorithm called DPLL (or DLL) is built (Code listing 1.1). Both the pseudocode and the algorithm description are based on [16]. The DPLL function is called with the whole formula and an empty set of variable assignments.

The process starts by deducing assignments from the current one. This is usually done using  $unit\ clause\ rule^1$  – if all but one literal of a clause were assigned value 0, the reminding one must be assigned value 1. In the deduction function, values of multiple variables can be deduced as assigning value to one can result in new unit clauses. During the deduction, if one variable should be assigned both 0 and 1 in order to satisfy different unit clauses, a conflict arises.

If the deduction finishes without a conflict, an unassigned variable is selected and assigned a value, and the algorithm calls itself recursively with the union of previous variable assignments and those assigned in the current step. If the deduction results in a conflict, the algorithm backtracks and tries different values for variables.

The algorithm ends if a satisfying variable assignment is found or if all possible assignments are checked (in this case, the formula is unsatisfiable). It can be extended to return a satisfying assignment as well.

#### **Code listing 1.1** DPLL algorithm pseudocode [16]

```

DPLL(formula, assignment) {

necessary = deduction(formula, assignment);

new_asgnmnt = union(necessary, assignment);

if (is_satisfied(formula, new_asgnmnt))

return SATISFIABLE;

else if (is conflicting(formula, new asgnmnt))

return CONFLICT;

var = choose_free_variable(formula, new_asgnmnt);

asgn1 = union(new_asgnmnt, assign(var, 1));

(DPLL(formula, asgn1) == SATISFIABLE)

return SATISFIABLE;

else {

asgn2 = union (new_asgnmnt, assign(var, 0));

return DPLL(formula, asgn2);

}

}

```

If we store assigned variables in the order they were assigned value, we can divide them into groups based on the decision level. Each manual value assignment creates a new decision level, and the manually assigned variable is the first variable on new level.

<sup>&</sup>lt;sup>1</sup>This rule is based on "Rule for the Elimination of One-Literal Clauses" [14]. However, it differs slightly as solvers do not eliminate variables with an assigned value, so it is an unsatisfied clause with one unassigned literal instead of a clause with only one literal. This clause is usually called unit clause.

Variables assigned values before any decision are on level 0 [17].

The algorithm can be rewritten into an iterative form, using checkpoint symbols to keep track of decision levels and to simulate the stack used in the recursive version. The iterative version has two main benefits: (1) it avoids creating a new stack each time a variable is manually assigned value [17], and (2) it enables non-chronological backtracking (i.e., returns more than one decision level at once). Non-chronological backtracking is described in the following subsection.

#### 1.2.2 Conflict-driven clause learning (CDCL)

Conflict-driven clause learning consists of two parts: clause learning and non-chronological backtracking. It extends and significantly improves the DPLL algorithm. It was introduced in 1996 in GRASP solver [18] and it is used by many modern solvers [17]. This description is based on [18].

The idea of clause learning is that conflicts are inevitable and that we can learn from the "mistakes" that led to them. If a conflict occurs, it is a result of some variable assignments the solver chose earlier (or that the formula is unsatisfiable). As variable assignments are either chosen by the solver or deduced from the choices (using the unit clause rule), we can find which choices of the solver lead to the conflict and learn a new clause from them. This clause consists of literals representing negations of variable assignments leading to the conflict. E.g., if assignments a = 0, b = 1, and c = 1 caused the conflict, the newly learned clause would be  $a \vee \neg b \vee \neg c$ .

The conflict can either result from the last chosen assignment (current decision level) or from the previous ones (lower decision levels). In the first case, it implies the opposite assignment of the last variable (if it has not been tried already). In the second case, the solver can backtrack to the highest decision level on which the conflict can yet be avoided. Multiple levels can be backtracked at once since conflict will always arise after assigning all variables leading to it. This second case is called *non-chronological backtracking* and can help to prune the search space significantly. If the solver backtracks before the first decision, the instance is proven unsatisfiable.

These methods speed up the solving of structured instances, i.e., the instances have some inner structure that does not depend on the instance size; industrial and real-world instances usually do have some structure. While solving random instances, they do not help [4].

# 1.3 Solvers used in the experimental part

In this section, solvers used in Chapter 2 are described. All three solvers use the CDCL algorithm, with the main differences being strategies for selecting the variable to assign a value to and for keeping/removing learned clauses and an approach to restarts.

The solvers are listed in order of their first appearance, from oldest to newest.

#### 1.3.1 **z**Chaff

ZCHAFF was created in 2001, improved in 2004 [4], and then slightly modified in 2007 [19].

The search procedure follows the standard conflict-driven idea utilizing backjumping. It uses a heuristic variable selection method called Variable State Independent Sum (VSIDS). It keeps scores for each literal of a variable, which is incremented each time a newly learned clause contains this literal. After a fixed time period, all scores are divided by 2. The score of a variable is greater of two associated literal scores. The variable with the highest score is assigned value – true if a positive literal has higher VSIDS and false otherwise.

zChaff uses methods to learn shorter clauses, which lead to faster clause propagation and can significantly prune the search space. Usage statistics and clause length are used to estimate its usefulness. Less useful clauses are periodically deleted.

Lastly, frequent restarts are used. After restarting, all VSIDS scores are set to 0, and the first variable is chosen arbitrarily [4].

#### 1.3.2 MiniSat

MINISAT is a small, efficient, and easily extendable SAT-solver. It was developed in 2003 and modified in the following years [20].

It uses a similar heuristic for selecting variables as ZCHAFF. Each variable is assigned an *activity* value, which is increased each time it appears in a new conflict clause. After each conflict, all *activity* values are multiplied by a constant smaller than 1. The unassigned variable with the highest activity is assigned a value first.

The clauses have *activity* is well. When a learned clause is used in the analysis of conflict, its *activity* is increased. Learned clauses with lower activity are periodically deleted. By default, MINISAT starts with a small set of learned clauses and gradually increases its size [5].

It also utilizes restarts to escape from hopeless parts of the search tree. The number of conflicts leading to restart increases during solving [5].

#### 1.3.3 Glucose

The Glucose [6] SAT-solver is based on MiniSat [5]. It was introduced in 2009 and was significantly improved in the following years.

The main extension is a new quality measure of learned clauses called Literal Block Distance (LBD). LBD is calculated as: "Given a clause c, and a partition of its literals into n subsets according to the current assignment, such that literals are partitioned w.r.t their decision level. The LBD of c is exactly n." Practical results show LBD is a very good indicator of learned clause usefulness [6].

To speed up clause propagation, the number of learned clauses is repeatedly halved so that their number slightly increases each time clauses are halved. Clauses with lower LBD are kept.

The restart policy is based on the quality of recently learned clauses, which has proven to be efficient in practice. When restarting, learned clauses remain. Moreover, if the solution seems to be near, the restart can be postponed.

An additional extension is parallel solving. Solvers solve the whole problem on each CPU separately and exchange the most useful learned clauses with each other [6].

Logic synthesis 10

#### 1.4 Logic synthesis

"Logic synthesis transforms HDL code into a netlist describing the hardware (e.g., the logic gates and the wires connecting them). The logic synthesizer might perform optimizations to reduce the amount of hardware required." [21]

A SAT instance can be seen as a circuit with one input for each variable and one output for the whole formula. This circuit can then be optimized using logic synthesis and transformed back to CNF using the Tseitin transformation [9] (see Subsection 1.1.1), hoping that the resulting SAT instance will be "easier" to solve.

In the experimental part (Chapter 2), the ABC tool [22] is used for synthesis. ABC is a public-domain tool for logic synthesis and verification. It uses And-Inverter Graphs<sup>2</sup> (AIGs) for representing circuits. Using AIG-based optimization repeated multiple times can be more efficient than approaches used by earlier tools while achieving the same or better results and using less memory and runtime, thus enabling its use on much larger circuits [23].

#### 1.5 Optimum circuit generation

An optimum circuit is a circuit representing a given k-variable Boolean function that is optimal in some aspect – usually has the minimum number of gates. Optimum circuits can be used in logic synthesis, e.g., the rewriting algorithm [24] repetitively rewrites subcircuits by their smaller, preferably optimum representations.

SAT-based method of generating the optimum circuit of a function is presented in [25]. The described procedure is as follows: for the k-variable function, start with n=1 and attempt to find optimum implementation using n gates by generating and solving a corresponding SAT instance; if the instance is unsatisfiable, such implementation does not exist, increase n by one and repeat the process; if the instance is satisfiable extract optimum circuit structure from it.

In Section 2.3, the use of logic synthesis on SAT instances created while generating optimum implementations of four- and five-variable functions is evaluated.

# 1.6 Automatic Test Pattern Generation (ATPG)

Automatic test pattern generation (ATPG) is a method of generating patterns (inputs) for testing the presence of defects in a physical circuit. It is possible to convert an ATPG instance into multiple SAT instances, which can then be solved by a SAT solver. If the SAT instance is satisfiable, a test pattern is extracted from the satisfying assignment. For unsatisfiable instances, no test pattern for the fault exists. This approach is called SAT-based ATPG [26].

In Section 2.4, the effectiveness of logic synthesis is evaluated on SAT instances generated by a simple SAT-based ATPG based on the original idea of Larrabee [26].

<sup>&</sup>lt;sup>2</sup>"An And-Inverter Graph is a directed acyclic graph (DAG), in which a node has either 0 or 2 incoming edges. A node with no incoming edges is a primary input (PI). A node with 2 incoming edges is a two-input AND gate. An edge is either complemented or not. A complemented edge indicates the inversion of the signal." [23]

Machine learning models and related topics used in evaluating practical use of synthesis

This approach generates conceptual hardware (*miter*) by XORing the fault-free and faulty circuit. This miter is then converted to a CNF by the Tseitin transformation [9] (see Subsection 1.1.1), and a test vector is generated as a satisfiability proof.

# 1.7 Machine learning models and related topics used in evaluating practical use of synthesis

In this section, machine learning (ML) models and related topics used in Chapter 3 are described. All described models are from the part of ML called supervised learning. This means that the desired outcomes are known. The opposite of supervised learning is unsupervised, where we do not know the outcomes, and the goal is to understand the structure of the data or some aspects of it [27].

In supervised learning, models are trained on many pairs of data–annotation to predict some target value (e.g., predict a digit from an image consisting of pixel data). The ability of the model is evaluated using some metric (e.g., ratio of correctly predicted digits). The goal is generalization – to create a model performing as well as possible on previously unseen data [27].

The two most common ML tasks are classification and regression. In classification, the model predicts one of multiple classes, while in regression, a real (continuous) value is predicted. Some models can be used for both tasks only with small modifications, while others can only be used for one of them.

#### 1.7.1 Model training and evaluation

There are two main methods of using data for training and evaluating models. The simpler one divides the dataset into three parts: training, development, and test sets. Models are trained on the training set. The development set is used to compare different models and hyperparameters and to select the best one, and the test set is used to evaluate the best model's generalization ability (i.e., the ability to predict on previously unseen data). This approach is used in most cases; however, if the dataset is small, it might be better to use cross-validation [28].

The basic method of cross-validation is k-fold cross-validation, which divides the data into k similarly sized parts. Then k models are trained and evaluated. Each one is trained on k-1 parts of the data and evaluated on the remaining one (each part is used for evaluation only once). The results of the model on the evaluation parts are then averaged together [28].

There are two approaches to selecting the best model using cross-validation. Firstly, the data can be divided into two sets: a training set and a test set. The best model is selected using cross-validation on the training set, and its generalization ability is evaluated on the test set. Secondly, if we do not want to divide the test set, we can use nested cross-validation to select the best model and evaluate it. An inner cross-validation is used to select the best model, and the outer is used to evaluate it. The average of evaluation results on outer cross-validation is then returned [29].

#### 1.7.2 Linear regression

Linear regression is one of the simplest models in machine learning. It is used for regression. It models linear relation between the data and targets. Interestingly, an exact formula for calculating weights of the model exists: for data  $X \in \mathbb{R}^{m,n}$  (m samples of n features) and targets  $Y \in \mathbb{R}^{m,1}$ , weights of the model are  $\mathbf{w} = (X^T X)^{-1} X^T Y$ . Prediction for a point  $\mathbf{x}$  is then just  $\hat{Y} = \mathbf{x}^T \mathbf{w}$  [30].

The power of this simple model can be extended by using some non-linear transformations (power, log, sin) of the features. It can also be limited by penalizing the size of model weights – preferring smaller and simpler models [30].

#### 1.7.3 Logistic regression

Logistic regression is a modification of linear regression used for binary classification. This model predicts a real number, which is then mapped into [0,1] interval using the sigmoid function,  $\sigma(x) = \frac{e^x}{1+e^x}$ . This number is then interpreted as the probability of one of the classes, the probability of the other class is complementar [31].

Contrary to linear regression, there is no exact formula for calculating the model's weights, so they are found using numerical methods (e.g., using gradient descent) [31].

#### 1.7.4 Naive Bayes

Naive Bayes is a classification model that chooses a different approach than other models described in this section. Instead of predicting the probability of a class given some data (i.e.,  $p(C_k|\mathbf{x})$ ), using Bayes' theorem, it models data distribution for each class, and in combination with the probability of each class, it predicts the most likely one (i.e.,  $\arg\max_k p(\mathbf{x}|C_k)p(C_k)$ ). Since modeling  $p(\mathbf{x}|C_k)$  is difficult, naive Bayes assumes all features to be independent so that  $p(\mathbf{x}|C_k) = \prod_{d=1}^n p(x_d|C_k)$  which can be modeled easier [32].

The distribution of each feature is modeled for each class independently. Normal, Bernoulli or multinomial distributions can be used for this purpose; the parameters of each distribution are calculated from data with the corresponding class. By choosing one of the distributions, we assume that features are from that distribution [32].

# 1.7.5 K-nearest neighbours

K-nearest neighbors is a simple model that can be used for both classification and regression. As is written in the name, it uses the nearest neighbors of a point to predict its value [32].

Its training is trivial – the training data are the model, and the training targets are the values of each training sample. Nevertheless, it has multiple hyperparameters that influence the model's predictions. The main ones are the number of neighbors used for predicting, metrics used for measuring distance, and weights of the neighbors (e.g., uniform or inverse to the distance) [32].

During prediction, k nearest neighbors of the given point are found. In the case of classification, the weights of neighbors are summed for each class separately, and the

Machine learning models and related topics used in evaluating practical use of synthesis

class with the highest sum is chosen. In regression, the prediction is the weighted average of the neighbors [32].

#### 1.7.6 Decision tree

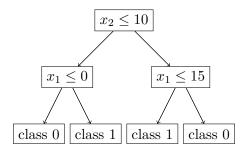

The decision tree divides the feature space into smaller parts, and each part is then handled separately. The model is a binary tree with internal nodes splitting data into two parts based on a simple condition on one of the features, e.g.,  $x_3 \leq 10$ . The leaves are used for predicting: in classification, the majority class of leaf samples is predicted; in regression, prediction is the average of the samples [33].

Prediction of a decision tree is just following the path from the root to a leaf; if the condition in the node is met, go to the left node; otherwise, to the right one. An example of decision tree is in Figure 1.1; for  $\mathbf{x} = (1, 20)^T$  model would predict class 1 [33].

If the tree had unlimited depth, it would be an index of the data. Since this is usually not wanted, hyperparameters such as maximum depth, minimum samples to split, or maximum number of leaf nodes are used [33].

**Figure 1.1** Example of decision tree for binary classification

#### 1.7.7 Random forest

Random forest consists of a collection of decision trees and combines their predictions — majority voting for classification, and an average for regression [33]. The idea is that by aggregating the results of many (smaller) models, the error will be smaller than of each individual model [34]. It can be used for both classification and regression.

During training, each tree is usually trained on a bootstrapped dataset in order to create diverse trees. The main hyperparameters are the number of trees in the model and the parameters of the trees [33].

## 1.7.8 Gradient boosting decision trees

The gradient boosting decision trees uses a collection of decision trees similarly to random forest. However, in this case, models are trained sequentially and new trees attempt to correct errors of the previous ones. This model can be used for both classification and regression [35].

As with the *random forest*, the main hyperparameters are the number of trees in the model and the parameters of the trees.

#### 1.7.9 Data preprocessing (feature normalization)

In some cases, it is beneficial for features to have similar sizes. E.g., when using k-nearest neighbors, if one feature is in thousands while the other is between zero and one, the smaller one will have almost no impact on which points are the nearest neighbors.

In order to train and use the model on values of features that have similar sizes, data can be preprocessed. Two commonly used methods are:

Normalization – scaling all features to [0, 1] interval using:  $x_{i,j}^{norm} = \frac{x_{i,j} - min_k x_{k,j}}{max_k x_{k,j} - min_k x_{k,j}}$

**Standardization** – scaling all features to have zero mean and standard deviation of one using:  $x_{i,j}^{standard} = \frac{x_{i,j} - \hat{\mu}_j}{\hat{\sigma}_i}$

#### 1.8 Usage of logic synthesis in SAT-solving

Using synthesis to speed up SAT-solving is not a novel idea. It has already been explored by [1] and [2]. However, only a limited number of instances were tested in both studies.

The first study presents results of using synthesis for preprocessing integer factorization problem<sup>3</sup>, which is hard for a SAT solver. For synthesis, SIS tool [36] (predecessor of ABC [23]) is used and zChaff solved the instances. The paper presents the results of ten instances solved without preprocessing and with preprocessed using the *simplify* synthesis algorithm. On unsatisfiable instances (factorization of a prime is attempted), significant speedup was measured, while on the satisfiable ones (factorization exists), solving with synthesis led to worse results [1].

The second paper is from the authors of MINISAT solver and ABC synthesis tool. Two approaches DAG-aware circuit compression and technology mapping for lookup-table (LUT) based FPGAs are explored with the use of MINISAT solver. In total, 30 hard SAT instances consisting of hard industrial instances and those from SAT-Race 2006 were tested. Applying both techniques led to a 5x speedup (does not include synthesis time) when solving hard industrial instances. In the case of SAT Race instances, synthesis sped up some of them while slowing down others [2].

This thesis intends to explore this topic further by analyzing the influence of logic synthesis on the solving time of a larger number of instances (benchmark as well as practical ones) using multiple currently available solvers (MINISAT, ZCHAFF, GLUCOSE) and ABC logic synthesis tool. In cases where synthesis led to speedup, the possibility of effective use in practice is also analyzed.

<sup>&</sup>lt;sup>3</sup>Given an integer x find its factors p and q greater than 1, such that  $x = p \cdot q$ .

# Chapter 2

# **Experiments**

In this chapter, three case studies are evaluated: applying logic optimization to SAT instances obtained from (1) standard satisfiability benchmarks (SATLIB) [37], (2) instances obtained from SAT-based optimum circuits generator [25], and (3) SAT-ATPG instances. The influence of different logic optimization processes on the overall run-time is studied.

. . . . . . . . . . .

#### 2.1 Experimental Setup

Experiments were run on an Intel Xeon Gold 5218 (2.30GHz) processor with 4 GB of memory running Debian 11 or Debian 12. All solvers were run using one CPU core, and GLUCOSE was run on four CPU cores as well. For practical reasons, solvers had a time limit of 2000 seconds (real-time); solving was terminated if an instance was not solved within the limit. Solvers are in the text referred to using their names; in the case of GLUCOSE, the results using one CPU core are referred to as GLUCOSE or, in some cases, GLUCOSE (one CPU), and four CPU cores results are referred to as "GLUCOSE (4CPU)" or "Gl. 4cpu" in tables. All time values are CPU time unless specified otherwise.

Logic synthesis was done using ABC 1.01 [22]. Glucose-syrup 4.2.1 [6], zChaff 2007.3.12 [4], and MiniSat 2.2 [5] solvers solved the SAT instances.

As for the logic synthesis and optimization, the following ABC scripts were used, and they will be referred to in the subsequent text as follows:

- Just a simple conversion to an AND-inverter-graph (AIG) [22], without any optimization: st: strash;

- A simple technology-independent optimization, with different efforts: st-re2-[1, 2, 3]x; whole script repeated x times: st-resyn2;

- A powerful optimization and mapping into 2-input gates, with different efforts: 2-gate-[1, 5, 10, 15]x; the part between get and put (first and last command) repeated x times:

```

&get -n; &st; &synch2; &if -m -a -K 2; &mfs -W 10; &st; &dch; &if -m -a -K 2; &mfs -W 10; &put;

```

■ A powerful optimization and mapping into 6-input LUTs, with different efforts: 6-LUT-[1, 5, 10, 15]x; the part between get and put (first and last command) repeated x times:

```

&get -n; &st; &synch2; &if -m -a -K 6; &mfs -W 10; &st; &dch; &if -m -a -K 6; &mfs -W 10; &put;

```

In experiments where a SAT instance in CNF was the source (i.e., Section 2.2 and 2.3), the CNF had to be transformed to a format accepted by ABC – the BLIF [38] and then, after the optimization, converted back to the CNF. The first conversion involved rewriting the CNF to a two-level network of a product of sums. The Tseitin transformation did the latter conversion [9] (see Subsection 1.1.1). An in-house tool was used for this purpose.

In the case of SAT solving with synthesis, only the *synthesis time and subsequent SAT solving time are considered* and compared to solving without synthesis. The time of file conversion from CNF to BLIF and back is not taken into account, as the tool used them is not optimized for speed.

#### 2.2 SATLIB benchmark instances

The SATLIB benchmark [37] offers a number of randomly generated hard 3-SAT instances, i.e., instances with the ratio of clauses to variables near 4.3 [39] and many other instances from different problem domains.

From available categories, only those with instances that took longer to solve were selected. Those are uniform Random-3-SAT instances with the numbers of variables and clauses equal to 200-860, 225-960, and 250-1065, as well as SAT-encoded Quasigroup (Latin square) instances and Pigeon-hole problem instances.

#### 2.2.1 Synthesis influence on CNF properties

Tables 2.9, 2.10, and 2.11 show how the synthesis and Tseitin transformation influenced the number of variables, number of clauses, and their ratio, respectively. Interestingly, many unsatisfiable instances from the first group of instances were transformed into trivial ones (i.e., for variable a, the CNF would be  $a \land \neg a$ ). The numbers of such instances are in Table 2.12. It happened mostly with 6-LUT-[1, 5, 10, 15]x syntheses and in the case of Quasigroup and Pigeon-hole instances with 2-gate-[1, 5, 10, 15]x synthesis as well. Repeating the synthesis script led to higher numbers of trivial instances. With the increasing complexity of uniform Random-3-SAT instances, the number of trivial instances decreases as the instances were probably too complex for synthesis to "solve" them.

If the trivial instances are left out, the average number of clauses increased significantly for almost all syntheses, with the exception of  $6\text{-}LUT\text{-}[5,\ 10,\ 15]x$  syntheses on the smallest uniform Random-3-SAT instances, and Pigeon-hole instances with  $2\text{-}gate-[5,\ 10,\ 15]x$  and  $6\text{-}LUT\text{-}[1,\ 5,\ 10,\ 15]x$  syntheses, which were all transformed into trivial ones.

Similarly, if the trivial instances are left out, the use of all syntheses led to a significant increase in the average number of variables, of course, with the exception of cases where all instances are transformed into trivial ones.

The more complex syntheses or their repetitions (2-gate-[1, 5, 10, 15]x and 6-LUT-[1, 5, 10, 15]x) led to a lower number of variables and clauses compared to other synthesis or less repetitions of the same script.

Although the number of clauses and variables mostly increased, their ratios usually decreased. In the case of uniform Random-3-SAT, with all syntheses except 6-LUT-[1, 5, 10, 15]x, the ratio changed from 4.3 to 2.7–2.8 with negligible standard deviations. With 6-LUT-[1, 5, 10, 15]x syntheses, the ratio gradually increases as the 3-SAT instances get larger; this happens even if trivial instances are left out.

The original clause-to-variable ratio of Quasigroup instances of  $74.1 \pm 85.3$  decreased with all syntheses significantly to 2.8-6.7 and a much lower standard deviation as well (at most 2.2). Lastly, Pigeon-hole instances clause-to-variable was originally 4.1, and in cases where resulting instances were not trivial ones, the ratio was, on average, around 2.1-2.7.

| Table | <b>2.1</b> SAT | TLIB 1 | benchma | ırk: ir | ıfluence | of logic | synthesis | on number  | of v | <i>r</i> ariables |

|-------|----------------|--------|---------|---------|----------|----------|-----------|------------|------|-------------------|

| Pro   | blem type      | 3-SAT  | 200-860 | 3-SAT   | 225-960  | 3-SAT 2  | 250-1065  | Quasigroup |      | Pigeon-ho         |

| Problem type  | 3-SAT 200-860     | 3-SAT 225-960     | 3-SAT 250-1065    | Quasigroup              | Pigeon-hole       |

|---------------|-------------------|-------------------|-------------------|-------------------------|-------------------|

| # instances   | $199^{1}$         | 200               | 200               | 22                      | 5                 |

| Original      | 200.0             | 225.0             | 250.0             | $1043.2 \pm 574.3$      | $74.0 \pm 26.9$   |

| st            | $2772.3 \pm 2.6$  | $3097.1 \pm 2.4$  | $3437.0 \pm 2.8$  | $161177.4 \pm 123534.2$ | $773.0 \pm 391.3$ |

| st-re2-1x     | $2716.1 \pm 7.7$  | $3039.4 \pm 8.2$  | $3373.0 \pm 8.3$  | $101578.3 \pm 64170.8$  | $467.0 \pm 197.8$ |

| st-re2-2x     | $2699.3 \pm 11.7$ | $3021.1 \pm 11.0$ | $3344.3 \pm 11.1$ | $100150.1 \pm 63138.6$  | $459.0 \pm 195.2$ |

| st-re2-3x     | $2687.0 \pm 16.6$ | $3005.2 \pm 14.8$ | $3319.3 \pm 13.9$ | $99692.7 \pm 62791.3$   | $456.0 \pm 197.6$ |

| 2-gate-1x     | $2678.9 \pm 8.3$  | $3004.4 \pm 8.8$  | $3339.6 \pm 8.8$  | $93769.2 \pm 71918.8$   | $148.2 \pm 329.1$ |

| 2-gate- $5x$  | $2529.7 \pm 12.0$ | $2846.6 \pm 11.9$ | $3163.0 \pm 11.8$ | $91215.3 \pm 70761.6$   | 1.0               |

| 2-gate- $10x$ | $2423.3 \pm 11.5$ | $2730.0 \pm 11.6$ | $3030.7 \pm 12.0$ | $90210.6 \pm 70434.0$   | 1.0               |

| 2-gate- $15x$ | $2361.7 \pm 9.9$  | $2661.1 \pm 10.6$ | $2950.2 \pm 11.0$ | $82938.0 \pm 74727.9$   | 1.0               |

| 6-LUT-1x      | $180.2 \pm 194.5$ | $601.4 \pm 315.2$ | $901.2 \pm 90.8$  | $25146.9 \pm 20706.8$   | 1.0               |

| 6-LUT- $5$ x  | $159.5 \pm 168.6$ | $471.6 \pm 314.2$ | $842.1 \pm 176.9$ | $23854.3 \pm 21167.3$   | 1.0               |

| 6-LUT- $10x$  | $157.1 \pm 165.2$ | $379.2 \pm 302.4$ | $791.6 \pm 222.1$ | $23646.9 \pm 21018.6$   | 1.0               |

| 6-LUT- $15x$  | $156.1 \pm 163.7$ | $354.4 \pm 292.4$ | $754.2 \pm 252.3$ | $22748.1 \pm 21415.0$   | 1.0               |

# 2.2.2 Synthesis influence on solving time

As tested instances had the upper time limit of 2000 seconds for the SAT-solver (see Section 2.1), some of them were not solved within the limit; if so, the process was terminated. Table 2.5 shows the numbers of instances of each combination of finished/terminated and with synthesis / without synthesis.

Table 2.6 shows ratios of instances whose time of solving improved after using logic synthesis. If an instance was solved both with and without synthesis, improvement was achieved only if the time of solving with synthesis (synthesis + SAT-solving) was smaller than solving without synthesis (only SAT-solving). If some instance was solved

<sup>&</sup>lt;sup>1</sup>This is not a mistake, in the benchmark instances archive are only 99 unsatisfiable instances in this category

**Table 2.2** SATLIB benchmark: influence of logic synthesis on number of clauses

| Problem type  | 3-SAT 200-860     | 3-SAT 225-960       | 3-SAT 250-1065      | Quasigroup              | Pigeon-hole         |

|---------------|-------------------|---------------------|---------------------|-------------------------|---------------------|

| # instances   | 199               | 200                 | 200                 | 22                      | 5                   |

| Original      | 860.0             | 960.0               | 1065.0              | $58469.7 \pm 42171.1$   | $322.0 \pm 170.3$   |

| st            | $7717.8 \pm 7.7$  | $8617.3 \pm 7.3$    | $9562.0 \pm 8.3$    | $480403.7 \pm 370199.3$ | $2098.0 \pm 1093.2$ |

| st-re2-1x     | $7549.4 \pm 23.0$ | $8444.3 \pm 24.7$   | $9369.9 \pm 24.8$   | $301606.4 \pm 191564.8$ | $1180.0 \pm 512.6$  |

| st-re2-2x     | $7498.9 \pm 35.2$ | $8389.4 \pm 33.0$   | $9283.8 \pm 33.3$   | $297321.9 \pm 188461.8$ | $1156.0 \pm 505.0$  |

| st-re2-3x     | $7462.0 \pm 49.7$ | $8341.7 \pm 44.4$   | $9208.9 \pm 41.8$   | $295949.6 \pm 187414.9$ | $1147.0 \pm 512.0$  |

| 2-gate-1x     | $7437.7 \pm 25.0$ | $8339.1 \pm 26.3$   | $9269.7 \pm 26.5$   | $281540.3 \pm 216567.1$ | $378.0 \pm 840.8$   |

| 2-gate- $5x$  | $6990.0 \pm 36.1$ | $7865.8 \pm 35.8$   | $8740.0 \pm 35.4$   | $274069.4 \pm 213224.6$ | 2.0                 |

| 2-gate- $10x$ | $6670.9 \pm 34.6$ | $7516.1 \pm 34.7$   | $8343.2 \pm 35.9$   | $271034.2 \pm 212256.6$ | 2.0                 |

| 2-gate- $15x$ | $6486.2 \pm 29.8$ | $7309.4 \pm 31.8$   | $8101.7 \pm 32.9$   | $248910.7 \pm 225150.1$ | 2.0                 |

| 6-LUT-1x      | $539.6 \pm 891.5$ | $3750.8 \pm 2330.6$ | $6205.7 \pm 638.1$  | $180036.6 \pm 141421.9$ | 2.0                 |

| 6-LUT- $5x$   | $411.9 \pm 615.6$ | $2549.4 \pm 2078.0$ | $5257.1 \pm 1143.7$ | $170474.2 \pm 145506.0$ | 2.0                 |

| 6-LUT-10x     | $392.0 \pm 575.8$ | $1779.9 \pm 1798.7$ | $4569.4 \pm 1377.3$ | $168269.8 \pm 144417.7$ | 2.0                 |

| 6-LUT-15x     | $384.5 \pm 560.4$ | $1569.9 \pm 1656.3$ | $4183.8 \pm 1497.8$ | $160829.6 \pm 147639.6$ | 2.0                 |

**Table 2.3** SATLIB benchmark: influence of logic synthesis on clause-variable ratio

| Problem type  | 3-SAT 200-860 | 3-SAT 225-960 | $3-SAT\ 250-1065$ | Quasigroup      | Pigeon-hole   |

|---------------|---------------|---------------|-------------------|-----------------|---------------|

| # instances   | 199           | 200           | 200               | 22              | 5             |

| Original      | 4.3           | 4.3           | 4.3               | $74.1 \pm 85.3$ | $4.1 \pm 0.8$ |

| st            | 2.8           | 2.8           | 2.8               | 3.0             | 2.7           |

| st-re2-1x     | 2.8           | 2.8           | 2.8               | 3.0             | 2.5           |

| st-re2-2x     | 2.8           | 2.8           | 2.8               | 3.0             | 2.5           |

| st-re2-3x     | 2.8           | 2.8           | 2.8               | 3.0             | 2.5           |

| 2-gate-1x     | 2.8           | 2.8           | 2.8               | $2.9 \pm 0.3$   | $2.1 \pm 0.2$ |

| 2-gate- $5x$  | 2.8           | 2.8           | 2.8               | $2.9 \pm 0.3$   | 2.0           |

| 2-gate- $10x$ | 2.8           | 2.8           | 2.8               | $2.9 \pm 0.3$   | 2.0           |

| 2-gate- $15x$ | 2.7           | 2.7           | 2.7               | $2.8 \pm 0.4$   | 2.0           |

| 6-LUT-1x      | $2.3 \pm 1.0$ | $5.2 \pm 2.1$ | $6.8 \pm 0.5$     | $6.7 \pm 1.7$   | 2.0           |

| 6-LUT- $5x$   | $2.2 \pm 0.8$ | $4.2 \pm 1.9$ | $6.1 \pm 0.9$     | $6.3 \pm 2.1$   | 2.0           |

| 6-LUT-10x     | $2.1 \pm 0.7$ | $3.5 \pm 1.7$ | $5.5\pm1.1$       | $6.2 \pm 2.1$   | 2.0           |

| 6-LUT-15x     | $2.1 \pm 0.7$ | $3.3 \pm 1.6$ | $5.2 \pm 1.2$     | $5.9 \pm 2.2$   | 2.0           |

with synthesis but not without it, it is considered to be sped up as well. However, if the time of solving with synthesis (synthesis + SAT-solving) is above the time limit for the SAT solver (2000 real-time seconds (corresponds to 8000 CPU seconds for Glucose (4CPU))). It cannot be decided whether the solving was sped up; in such case, the ratio of improved instances is presented as a range. Instances that were solved neither with nor without synthesis are left out.

The influence of synthesis on the solving time is shown in Table 2.7 and 2.8. The percentage changes are calculated based on instances that were finished both with and without synthesis within the time limit. The number of such instances is the first value of the corresponding cell in Table 2.5. This approach results in possibly different instances being used for calculating the percentage changes for different combinations of solver and synthesis, which, in some cases, causes worse comparability if many instances are left out. We chose this approach as the number of instances that were solved by all solvers

| Problem type      | 3-SAT 200-860 | 3-SAT 225-960 | 3-SAT 250-1065 | Quasigroup | Pigeon-hole |

|-------------------|---------------|---------------|----------------|------------|-------------|

| # UNSAT instances | 99            | 100           | 100            | 12         | 5           |

| st                | 0             | 0             | 0              | 0          | 0           |

| st-re2-1x         | 0             | 0             | 0              | 0          | 0           |

| st-re2-2x         | 0             | 0             | 0              | 0          | 0           |

| st-re2-3x         | 0             | 0             | 0              | 0          | 0           |

| 2-gate-1x         | 0             | 0             | 0              | 2          | 4           |

| 2-gate- $5x$      | 0             | 0             | 0              | 2          | 5           |

| 2-gate- $10x$     | 0             | 0             | 0              | 2          | 5           |

| 2-gate- $15x$     | 0             | 0             | 0              | 4          | 5           |

| 6-LUT-1x          | 97            | 37            | 2              | 2          | 5           |

| 6-LUT- $5x$       | 99            | 50            | 8              | 4          | 5           |

| 6-LUT- $10x$      | 99            | 64            | 13             | 4          | 5           |

| 6-LUT- $15x$      | 99            | 67            | 18             | 5          | 5           |

**Table 2.4** SATLIB benchmark: numbers of unsatisfiable instances which were transformed by synthesis into trivial ones (i.e., for variable a, the CNF would be  $a \land \neg a$ )

without synthesis and with all syntheses would sometimes be rather limited. Moreover, the main goal of this thesis is to evaluate the improvements achievable by synthesis, and this approach allows for individual results to be more precise as they are based on more instances.

Likewise, the average time shown in each column can be compared between solvers only if all instances (or most of them) were solved without synthesis. If some instances are left out (due to not being solved within the time limit), the real average time would be much higher than the presented one. Therefore, it usually offers only a rough idea about the solving time to which the percentage changes can be related. In case all instances were solved, which is for benchmark instances mostly true, all values are exact and can be compared easily.

In many cases, the average time of solving for different solvers in one category varies greatly. This, even with approximate results, means that a large potential improvement of using some synthesis would not usually be useful in practice as using the fastest solver (even without any synthesis) would result in a faster time.

The values in Table 2.7 are calculated using Equation 2.1 where (nosyn, syn) are pairs of solving time without synthesis (only SAT-solving of the original instance) and with synthesis (synthesis + SAT-solving). The values show how the original total time would change if synthesis were used only on instances when it decreased the overall time of solving that instance and others were solved without it. These values show how large improvement can be potentially achieved with each synthesis script on tested instances. On its own, it does not reflect any practical application. However, for synthesis to have practical use, a (high) potential decrease in solving time is a necessary condition. In the following paragraphs, mainly, this potential improvement is discussed.

$$\frac{\sum_{(time,syn)} min\{time,syn\}}{\sum_{(time,syn)} time} - 1 \tag{2.1}$$

Table 2.8 presents how solving time would be influenced by always using synthesis. In the category of smallest uniform Random-3-SAT instances (3-SAT 200-860), all