### TIME-AREA EFFICIENT HARDWARE ARCHITECTURES FOR CRYPTOGRAPHY AND CRYPTANALYSIS

#### Dissertation

zur

Erlangung des Grades eines

Doktor-Ingenieurs

der

Fakultät für Elektrotechnik und Informationstechnik an der Ruhr-Universität Bochum

> von Martin Novotný Bochum, Februar 2009

Author's contact information: novotnym@fit.cvut.cz

Thesis Advisor: Prof. Dr.-Ing. Christof Paar

Ruhr-University Bochum, Germany

Secondary Referee: Ing. Jan Schmidt, Ph.D.

CTU in Prague, Czech Republic

Thesis submission: February 2, 2009 Thesis defense: April 30, 2009

## Abstract

In the first part of the thesis we focus on scalable arithmetic units operating over the binary finite field  $GF(2^m)$  with a normal basis representation of the field elements. The scalability is crucial in applications of different kind – small, low power embedded devices as opposed to high-throughput backbone applications.

Although scaling by digit-serialization is a well-known method, its application to normal-basis multipliers brings problems with irregularities. Little has been done for the case when the digit width does not divide the degree of the field, although this situation is unavoidable in cryptographic applications.

In this thesis we present four architectures of the digit-serial normal basis multiplier that we developed. We demonstrate digit-serialization on the pipelined multiplier by Agnew et al., however, these methods are also applicable to other multiplier structures, e.g. the multiplier by Kwon et al. All architectures can be implemented for any digit width. Our evaluation shows that their advantages are complementary with respect to the digit width.

Based on the scalable multiplier design, we extended our work to build an entire scalable arithmetic unit. Only a shifter has to be added to support inversion. It is scaled by the number of shifts implemented in hardware. This is a special case of another little-studied problem: scaling a sub-unit in the presence of another one, dominating the design in area and time. We present an optimization method applicable to such cases.

In the second part of the thesis we focus on cryptanalysis of GSM communication, which is encrypted with A5/1 cipher. We present two attacks against A5/1 cipher. Both attacks are supported by an existing low-cost special-purpose hardware device COPACOBANA. They represent the first real-world implementations of attacks against A5/1 reported in open literature.

The first attack is a guess-and-determine attack revealing the internal state of A5/1 in about 6 hours on average (and about 12 hours at the worst-case). To mount the attack only 64 consecutive bits of a known keystream are required and we do not need any precomputed data. We also propose an optimized version of the attack. Both plain and optimized version of the attack have been fully implemented and tested on our target platform.

The second attack is a time-memory-data trade-off attack revealing the internal state of A5/1 with certain probability in a matter of minutes. COPA-COBANA is used in both the precomputation phase and the online phase of the attack. When designing the precomputation engine, we have utilized the features of underlying FPGA architecture to gain the maximum performance. Here proposed design approach can be reused when designing similar attacks against other stream ciphers.

#### **Keywords:**

Public Key Cryptography, Elliptic Curve Cryptography, Arithmetic Unit, Binary Finite Fields  $GF(2^m)$ , Normal Basis, Multiplication, Inversion, Cryptanalysis, Brute-Force Attack, TMDTO Attack, A5/1, COPACOBANA, FPGA

## Kurzfassung

Die vorliegende Dissertation gliedert sich thematisch in zwei Teile. Der erste Teil beschäftigt sich mit skalierbaren Arithmetikeinheiten über endlichen Körpern der Form  $GF(2^m)$  in Normalbasis-Repräsentation. Die Skalierbarkeit dieser Architekturen ist dabei essentiell, um den Anforderungen unterschiedlicher Anwendungen – zum Beispiel kleine, eingebettete Systeme mit geringer Leistungsaufnahme im Gegensatz zu Backbone-Systemen mit hohem Datendurchsatz – gerecht zu werden.

Skalierung durch Serialisierung ist eine wohlbekannte Methode, jedoch bringt ihre Anwendung auf Normalbasis-Multiplizierer Probleme durch bestimmte Irregularitäten mit sich. In der einschlägigen Literatur wurde der Fall, dass die Wortbreite kein Teiler des Erweiterungsgrades ist, so gut wie nicht behandelt, obwohl dieser Fall für kryptographische Anwendungen praktisch unvermeidbar ist.

In dieser Arbeit werden vier neuartige "digit-serial" Normalbasis-Multiplizierer vorgestellt. Dabei handelt es sich um serialisierte Varianten des Multiplizierers von Agnew et al. Es ist erwähnenswert, dass die dazu entwickelten Serialisierungsmethoden auch auf anderere Architekturen, wie zum Beispiel den Multiplizierer von Kwon et al., angewandt werden können. Alle vorgestellten Architekturen können für beliebige Wortbreiten implementiert werden. Die durchgeführte Evaluierung zeigt, dass die Vorteile der Architekturen sich hinsichtlich der Wortbreite komplementär verhalten.

Als weiterer Forschungsbeitrag wird eine vollständig skalierbare Arithmetikeinheit entwickelt, die auf den vorgestellten Multiplizierern basiert. Diese Einheit wurde darauf optimiert möglichst wenig Chipfläche einzunehmen und ist in der Tat nur unwesentlich größer als der enthaltene Multiplizierer. In diesem Kontext stellt sich das bisher wenig untersuchte Problem der Dimensionierung eines Bausteins in der Gegenwart eines zweiten, der das Gesamtsystem

bezüglich Fläche und Zeit dominiert. Eine allgemeine Optimierungsstrategie für derartige Fälle wird vorgeschlagen.

Der zweite Teil dieser Arbeit beschäftigt sich mit der hardware-basierten Kryptanalyse der im GSM-Mobilfunknetz eingesetzten Stromchiffre A5/1. Basierend auf dem kürzlich vorgestellten, kosteneffizienten FPGA-Cluster CO-PACOBANA werden zwei Angriffe gegen A5/1 realisiert. Im Gegensatz zu bisherigen Arbeiten handelt es sich hierbei um zwei äußerst praktikable und vollständig implementierte Attacken.

Der erste Angriff fällt in die Klasse der sogenannten "guess-and-determine" Attacken und ist in der Lage den geheimen internen Zustand der Chriffre in durchschnittlich 6 Stunden (12 Stunden im "worst-case") zu bestimmen. Um diesen Angriff durchzuführen werden nur 64 (aufeinanderfolgende) Bits des Schlüsselstroms und keinerlei Vorberechnungen benötigt. Die vorgeschlagene Attacke, sowie eine optimierte Variante wurden komplett auf COPACOBANA implementiert und getestet.

Beim zweiten Angriff handelt es sich um eine "time-memory-data tradeoff" Attacke. Mittels der entwickelten hardware-basierten Realisierung dieses

Angriffs kann, mit einer gewissen aber signifikanten Wahrscheinlichkeit, der

Initialzustand von A5/1 innerhalb von Minuten wiederhergestellt werden. Die

Spezialhardware COPACOBANA wird sowohl für die benötigten (umfangreichen) Vorberechnungen als auch für den eigentlichen Angriff eingesetzt. Idealerweise könnte das hier vorgeschlagene Design als Referenz für gleichartige

Angriffe auf Stromchiffren dienen.

#### Schlüsselworte:

Public-Key-Kryptographie, Elliptische-Kurven-Kryptographie, Hardwarearithmetik, Endliche Körper, Normalbasen, Multiplikation, Inversion, Kryptanalyse, Brute-Force Attacken, TMDTO Attacken, A5/1, COPACOBANA, FPGA

## Acknowledgements

First of all, I would like to thank to both my supervisors, Christof Paar and Jan Schmidt.

I would like to thank Jan Schmidt for initiating my research, for sometimes pushing me to do the right things, and for overall support. Without his ideas, help and collaboration, the first part of this thesis would be infeasible.

Christof Paar gave me the opportunity to join his research group for 18 months. The experience I got in the fruitful atmosphere of the group is unique. Christof's constant encouragement and effort as the thesis supervisor contributed substantially to the quality and completeness of the thesis. I am also grateful for his generous help with the funding of my stay.

Finishing this thesis would be infeasible without the help of Irmgard Kühn. She was generous with her help and support during my whole research stay. Horst Edelmann helped me with all technical problems and gave me good tips for trips around the Ruhr Area.

Tim Güneysu and Jan Pelzl initiated my stay in Bochum. With Tim, we worked on COPACOBANA-related problems. Andy Rupp, Timo Gendrullis and I collaborated on cryptanalysis of A5/1. We also discussed some problems with Andrey Bogdanov. Our work led to the results which are summarized in the second part of this thesis.

I had the privilege to share a lot of fun with Timo Kasper. I still reminisce the voyages which we made with Francesco Regazzoni to explore the Ruhr Area and Germany. Thanks to Amir Moradi and his wife Shakila I could extend my knowledge about culture and life of people in different parts of the world. I would also like to extend my thanks to Axel Poschmann, Thomas Eisenbarth, Marko Wolf, Kerstin Lemke-Rust and many others.

I am also thankful to my landlord Mr. Falke and his family. Their house in Bochum became my second home for the whole period of my stay.

I am grateful to the head of our department, Hana Kubátová, for her unconditional help and support. Jiří Douša and Alois Pluháček were my great teachers who became my colleagues. I am also glad to have colleagues who create a cosy environment, namely Petr Fišer, Radek Dobiáš and Pavel Kubalík.

My thanks also go to many other people whom I forgot to mention, but who helped me in my life and work or who simply make this world better.

However, my greatest thanks go to my family. It is my parents who provided for my education and who have been supporting me throughout the my whole life. My nephews Ondřej and Marek, sons of my brother and my wonderful sister-in-law, are a constant source of happiness. My partner Mirek encouraged me to get the experience in Bochum. The 18 month I spent there, far away from home, were hard period for both of us, but Mirek has shown extraordinary patience, love and support.

Thank you!

To my partner and my family.

## Contents

|        | List | of Ta   | bles                                                                | xix  |

|--------|------|---------|---------------------------------------------------------------------|------|

|        | List | of Al   | $_{ m gorithms}$                                                    | xxi  |

|        | List | of Fig  | gures                                                               | xxii |

| 1      | Intr | roduct  | ion                                                                 | 1    |

| I<br>B |      | _       | Methods for Scalable Arithmetic Units over<br>lds with Normal Basis | . 3  |

| 2      | Intr | roducti | ion to Part I                                                       | 5    |

| 3      | Ma   | thema   | tical Background                                                    | 9    |

|        | 3.1  | Ellipti | ic Curves                                                           | 9    |

|        | 3.2  | Ellipti | ic Curves over Binary Finite Fields, $GF(2^m)$                      | 11   |

|        | 3.3  | Opera   | tions on Binary Field, $GF(2^m)$                                    | 13   |

|        | 3.4  | Opera   | tions on $GF(2^m)$ with a Normal Basis Representation               | 14   |

|        |      | 3.4.1   | Addition                                                            | 14   |

|        |      | 3.4.2   | Multiplication                                                      | 14   |

|        |      | 3.4.3   | Squaring                                                            | 16   |

|        |      | 3.4.4   | Division/Inversion                                                  | 17   |

| 4 | $\mathbf{Pre}$ | vious work                                                                  | 19 |

|---|----------------|-----------------------------------------------------------------------------|----|

|   | 4.1            | Massively Parallel Multiplier                                               | 19 |

|   | 4.2            | Massey-Omura Multiplier                                                     | 20 |

|   | 4.3            | Pipelined Massey-Omura Multiplier                                           | 20 |

|   | 4.4            | Other Multipliers                                                           | 24 |

|   | 4.5            | Digit-Serial Multiplier                                                     | 25 |

| 5 | Mu             | tiplication/Inversion Unit                                                  | 31 |

|   | 5.1            | Structure of the Unit                                                       | 32 |

|   |                | 5.1.1 Multiplication                                                        | 33 |

|   |                | 5.1.2 Inversion                                                             | 34 |

|   |                | 5.1.3 Division                                                              | 36 |

|   | 5.2            | Throughput Improvement of the Unit                                          | 36 |

|   |                | 5.2.1 Digit-Serialization of the Multiplier                                 | 37 |

|   |                | 5.2.2 Modification of the Shifter                                           | 38 |

|   | 5.3            | Implementation Results                                                      | 42 |

|   |                | 5.3.1 Effect of a Digit-Serialization of the Multiplier $\ \ldots \ \ldots$ | 42 |

|   |                | 5.3.2 Iterative Squarings Improvement in the Shifter $\dots$                | 44 |

|   | 5.4            | Summary and Final Remarks                                                   | 44 |

| 6 | Dig            | it-Serial Multipliers of a General Digit Width                              | 47 |

|   | 6.1            | Circular Multiplier (GC)                                                    | 48 |

|   | 6.2            | Linear Multiplier (GL)                                                      | 50 |

|   | 6.3            | End-Correction Multiplier (GCEC)                                            | 54 |

|   | 6.4            | Circular Multiplier with Distributed Overlap (GCDIST and GCDO)              | 58 |

|   | 6.5            | Area and Critical Path Length                                               | 62 |

|   |                | 6.5.1 Bit-Serial Multiplier                                                 | 63 |

|   |                | 6.5.2 Standard Digit-Serial Multiplier                                      | 63 |

|   |                | 6.5.3 Circular Digit-Serial Multiplier                                      | 64 |

|   |                | 6.5.4 Linear Digit-Serial Multiplier                                        | 64 |

|         |                             | 6.5.5                                                                     | End-Correction Digit-Serial Multiplier               | 64                                         |

|---------|-----------------------------|---------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------|

|         |                             | 6.5.6                                                                     | Circular Multiplier with Distributed Overlap $\dots$ | 64                                         |

|         | 6.6                         | Imple                                                                     | mentation Results                                    | 64                                         |

| 7       | Sca                         | lable S                                                                   | Shifter Synthesis                                    | 73                                         |

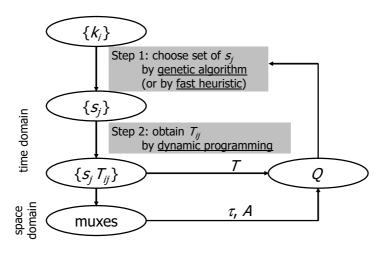

|         | 7.1                         | Proble                                                                    | em Formulation                                       | 73                                         |

|         | 7.2                         | Appro                                                                     | each Overview                                        | 76                                         |

|         |                             | 7.2.1                                                                     | Sub-optimum Rotation Set by a Genetic Algorithm      | 77                                         |

|         |                             | 7.2.2                                                                     | Sub-optimum Rotation Set by a Fast Heuristic         | 77                                         |

|         | 7.3                         | Result                                                                    | S                                                    | 78                                         |

|         |                             | 7.3.1                                                                     | Future Work                                          | 78                                         |

|         |                             |                                                                           | 7.3.1.1 Reformulating the Observation 2              | 79                                         |

|         | 7.4                         | Summ                                                                      | ary                                                  | 81                                         |

| TT      |                             |                                                                           |                                                      |                                            |

|         |                             | OPA cation                                                                | COBANA-Assisted Attacks on GSM Com-                  | 85                                         |

|         | unio                        | cation                                                                    |                                                      |                                            |

| m<br>9  | unic<br>Intr                | cation                                                                    | ion to Part II                                       | 85                                         |

| m<br>9  | unio<br>Intr<br>Bac         | cation<br>coduct                                                          | ion to Part II                                       | 85<br>87                                   |

| m<br>9  | Intr<br>Bac<br>10.1         | cation<br>coducts<br>kgroun<br>A5/1                                       | ion to Part II                                       | <ul><li>85</li><li>87</li><li>89</li></ul> |

| m<br>9  | Intr<br>Bac<br>10.1         | cation<br>coduct<br>kgroun<br>A5/1<br>Previo                              | ion to Part II  nd  Cipher                           | 85<br>87<br>89                             |

| m<br>9  | Intr<br>Bac<br>10.1         | cation<br>coducts<br>kgroun<br>A5/1<br>Previo                             | ion to Part II  ad Cipher                            | 85<br>87<br>89<br>89                       |

| m<br>9  | Intr<br>Bac<br>10.1<br>10.2 | cation<br>roducts<br>kgroun<br>A5/1<br>Previo<br>10.2.1<br>10.2.2         | ion to Part II  nd Cipher                            | 85<br>87<br>89<br>89<br>92                 |

| 9<br>10 | Intr<br>Bac<br>10.1<br>10.2 | cation<br>roducti<br>kgroun<br>A5/1<br>Previo<br>10.2.1<br>10.2.2<br>COPA | ion to Part II  nd Cipher                            | 85<br>87<br>89<br>89<br>92<br>94           |

| 9<br>10 | Intr<br>Bac<br>10.1<br>10.2 | kgroud A5/1 Previo 10.2.1 10.2.2 COPA                                     | ion to Part II  nd Cipher                            | 85<br>87<br>89<br>92<br>92<br>94<br>95     |

| 11.1.2 A Slight Modification                            | )2 |

|---------------------------------------------------------|----|

| 11.2 Hardware Architecture for COPACOBANA               | )6 |

| 11.2.1 The Guessing-Engine                              | )6 |

| 11.2.2 The Control-Interface                            | )7 |

| 11.2.3 Optimization: Storing Intermediate States 10     | )8 |

| 11.3 Implementation Results for COPACOBANA 11           | 1  |

| 11.4 Summary                                            | .3 |

| 12 Time-Memory Trade-off Attacks 11                     | .5 |

| 12.1 Original Hellman's Approach                        | 6  |

| 12.1.1 Basic Idea                                       | 7  |

| 12.1.2 Offline Phase                                    | 7  |

| 12.1.3 Online Phase                                     | 8  |

| 12.1.4 Characteristics                                  | 9  |

| 12.2 Distinguished Points                               | 21 |

| 12.2.1 Offline Phase                                    | 21 |

| 12.2.2 Online Phase                                     | 22 |

| 12.2.3 Characteristics                                  | 23 |

| 12.3 Time-Memory-Data Trade-off Attacks                 | 26 |

| 12.4 Rainbow Tables                                     | 27 |

| 12.4.1 Offline Phase                                    | 28 |

| 12.4.2 Online Phase                                     | 28 |

| 12.4.3 Characteristics                                  | 28 |

| 12.5 Thin-Rainbow Tables                                | 30 |

| 12.5.1 Thin-Rainbow Tables with Distinguished Points 13 | 30 |

| 12.5.2 Offline Phase                                    | 31 |

| 12.5.3 Online Phase                                     | 31 |

| 12.5.4 Characteristics                                  | 31 |

| 13 Time-Memory-Data Trade-off Attack on A5/1            | 5  |

| 13.1   | Table Precomputation                                                   | 36  |

|--------|------------------------------------------------------------------------|-----|

|        | 13.1.1 Chosen Method                                                   | 36  |

|        | 13.1.2 Design Approach                                                 | 36  |

|        | 13.1.3 The TMTO Element                                                | 38  |

|        | 13.1.4 Architecture of the Table Precomputation Engine 1               | 39  |

|        | 13.1.5 Data Transfer from COPACOBANA to the Host Computer              | 42  |

|        | 13.1.6 Selection of Parameters                                         | 43  |

| 13.2   | Fast Sort of Disk Stored TMTO Tables                                   | 43  |

|        | 13.2.1 Implemented Method                                              | 46  |

| 13.3   | Implementation Results — the Precomputation Phase 1                    | 47  |

|        | 13.3.1 Chains Merging One Step after the Start Point 1                 | 52  |

| 13.4   | Online Engine                                                          | 55  |

|        | 13.4.1 Online TMTO element                                             | 55  |

|        | 13.4.2 Architecture of the A5/1 Online Engine $\dots 1$                | 56  |

|        | 13.4.3 Implementation Results                                          | 59  |

| 13.5   | Fast Search at Disk-Stored TMTO Tables                                 | 60  |

| 13.6   | Summary and Final Remarks                                              | 62  |

| 14 Bac | ctracking A5/1                                                         | 65  |

| 14.1   | Detailed View on Algorithm of A5/1                                     | 65  |

| 14.2   | Previous Work                                                          | 67  |

| 14.3   | Proposed Method                                                        | 67  |

| 14.4   | Testing the Method for A5/1 Backtracking                               | 69  |

|        | 14.4.1 Test 1: Clocking A5/1 Forward and Backward for 101 Clock Cycles | .73 |

|        | 14.4.2 Test 2: Clocking A5/1 Forward and Backward for 151 Clock Cycles | .73 |

|        | 14.4.3 Test 3: Clocking A5/1 Backward Only for 101 Clock Cycles        | .73 |

|    | Cycles                              | 178 |

|----|-------------------------------------|-----|

|    | 14.5 Summary and Final Remarks      | 180 |

| 15 | Conclusions of Part II              | 181 |

|    | Acronyms and Symbols                | 183 |

|    | Bibliography                        | 190 |

|    | Refereed Publications of the Author | 191 |

|    | Curriculum Vitae                    | 193 |

## List of Tables

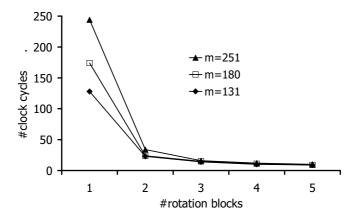

| 5.1  | The number of clock cycles required for squarings in ITT algorithm for various number of rotation blocks and for $m = 131$ , 180 and 251                                                                             | 39  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2  | $\label{lem:lementation} Implementation of the modified multiplier/inverter in the Xilinx \\ Virtex 300 \dots \dots$ | 43  |

| 6.1  | Hardware resources                                                                                                                                                                                                   | 65  |

| 6.2  | Critical path length                                                                                                                                                                                                 | 65  |

| 6.3  | Implementation results for $m=180$                                                                                                                                                                                   | 70  |

| 6.4  | Implementation results for $m=173$                                                                                                                                                                                   | 71  |

| 7.1  | Shifters Adjusted to Different Multipliers                                                                                                                                                                           | 79  |

| 10.1 | Clockcontrol of A5/1                                                                                                                                                                                                 | 91  |

| 11.1 | Implementation results for the control-interface and the guessing-engines                                                                                                                                            | 111 |

| 11.2 | Comparison of the implementation results of both guessing-engines                                                                                                                                                    | 112 |

| 11.3 | Implementation results of the maximally utilized designs                                                                                                                                                             | 112 |

|      | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                              | 144 |

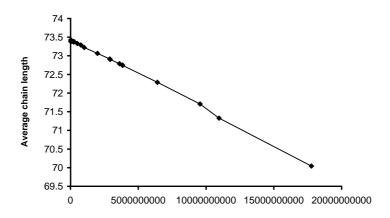

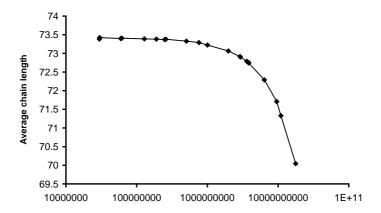

| 13.2 | Theoretical and measured values of the number of chains in the table $(\widehat{m})$ and their average length $(l'_{avg})$ after rejection of chains with duplicate end points                                       | 150 |

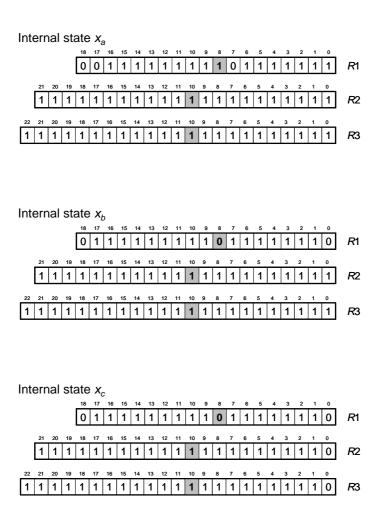

| 14.1 | Three examples of the internal states and the candidates for |     |

|------|--------------------------------------------------------------|-----|

|      | their predecessors. Clocking bits are highlighted            | 168 |

| 14.2 | Predecessors of the states — part 1                          | 170 |

| 14.3 | Predecessors of the states — part 2                          | 171 |

# List of Algorithms

| 3.1  | Normal basis multiplication                             | 16  |

|------|---------------------------------------------------------|-----|

| 3.2  | Itoh-Teechai-Tsujii inversion in $GF(2^m)$              | 17  |

| 5.1  | An implementation of the ITT inversion in a multiplica- |     |

|      | tion/inversion unit                                     | 35  |

| 14.1 | BACKWARD_STEP(R1, R2, R3, DEPTH) — a recurrent pro-     |     |

|      | cedure for A5/1 backtracking                            | 172 |

# List of Figures

| 3.1  | Point addition on an elliptic curve                                                                                            | 10 |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Massey-Omura multiplier                                                                                                        | 20 |

| 4.2  | Modification of the Massey-Omura multiplier by Agnew et al. Structure shown here is for $GF(2^6)$ and its optimal normal basis | 21 |

| 4.3  | Terms evaluated in the stages of the register $C$ in the bit-serial multiplier in the $k$ -th clock cycle                      | 23 |

| 4.4  | Evaluation of terms in pipelined bit-serial multiplier by Agnew et al. (for $GF(2^6)$ and its optimal normal basis)            | 24 |

| 4.5  | Evaluation of terms in pipelined bit-serial multiplier by Agnew et al. (for $GF(2^5)$ and its Type II optimal normal basis)    | 25 |

| 4.6  | Evaluation of terms in pipelined bit-serial multiplier by Kwon et al. (for $GF(2^5)$ and its Type II optimal normal basis)     | 26 |

| 4.7  | Evaluation of terms in the register $C$ in standard digit-serial multiplier, a) full notation, b) abbreviated notation         | 27 |

| 4.8  | Evaluation of the terms in a pipelined digit-serial multiplier (for $GF(2^6)$ and its optimal normal basis; digit width $D=2)$ | 29 |

| 4.9  | Evaluation of the terms in the stages of a digit-serial multiplier for $m=6$ and $D=2$                                         | 29 |

| 4.10 | Evaluation of the terms in the stages of a digit-serial multiplier for $m=6$ and $D=3$                                         | 29 |

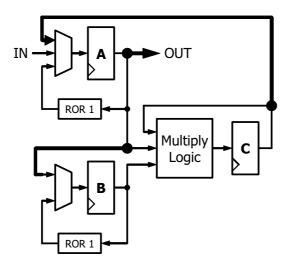

| 5.1  | Block diagram of the pipelined multiplier by Agnew et al                                                                       | 32 |

| 5.2  | Multiplication/inversion unit                                                                                                  | 33 |

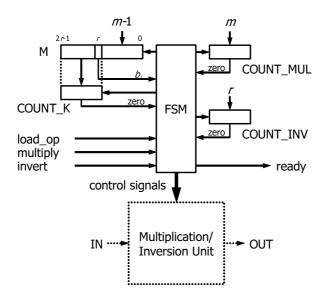

| 5.3        | Control unit for a multiplication/inversion unit                                                                                                                  | 34       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.4        | The number of clock cycles spent in squarings for various number of rotation blocks                                                                               | 39       |

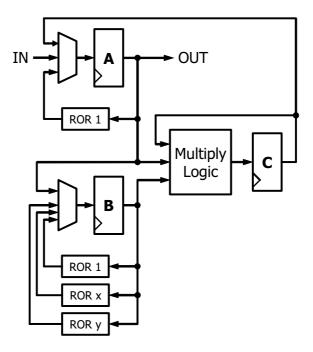

| 5.5        | "Long distance" rotations $ROR$ $x$ and $ROR$ $y$ save clock cycles necessary for squarings in ITT algorithm                                                      | 40       |

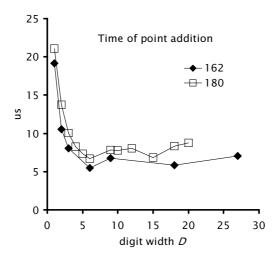

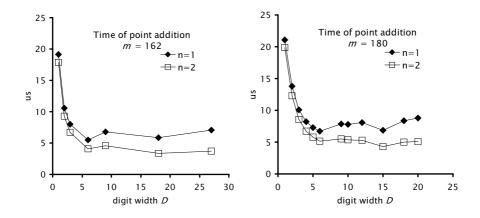

| 5.6        | Time of point addition for different digit widths. No "long distance" rotation blocks are used                                                                    | 42       |

| 5.7        | The effect of adding 1 rotation block, a) $m=162$ , b) $m=180$ .                                                                                                  | 44       |

| 6.1        | Circular Multiplier, GC                                                                                                                                           | 48       |

| 6.2        | Evaluation of the terms in the stages of the circular digit-serial multiplier for $m=11$ and $D=2$                                                                | 49       |

| 6.3        | Evaluation of the terms in the stages of the circular digit-serial multiplier for $m=11$ and $D=3.$                                                               | 49       |

| 6.4        | Linear Multiplier, GL                                                                                                                                             | 50       |

| 6.5        | Evaluation of the terms in the stages of a linear digit-serial multiplier for $m=11$ and $D=2,\ldots,\ldots$                                                      | 53       |

| 6.6        | Evaluation of the terms in the stages of a linear digit-serial multiplier for $m=11$ and $D=3$                                                                    | 53       |

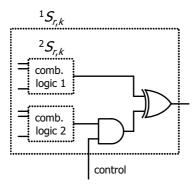

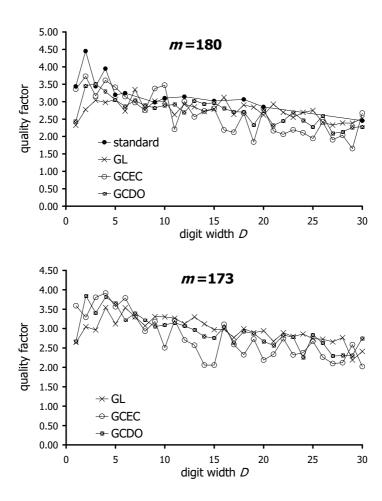

| 6.7        | The sum ${}^2S_{r,k}$ contains the subset of the terms from the sum ${}^1S_{r,k}$ , ${}^2S_{r,k} \subseteq {}^1S_{r,k}$ . In the last clock cycle, some terms are | 50       |

| <i>c</i> o | switched off                                                                                                                                                      | 56<br>56 |

| 6.8        | End-Correction Multiplier, GCEC                                                                                                                                   | 56       |

| 6.9        | Evaluation of the terms in the stages of the end-correction digit-<br>serial multiplier for $m=11$ and $D=2.\ldots$                                               | 58       |

| 6.10       | Evaluation of the terms in the stages of the end-correction digit-<br>serial multiplier for $m=11$ and $D=3,\ldots,\ldots$                                        | 58       |

| 6.11       | Evaluation of the terms in the stages of a circular digit-serial multiplier with a distributed overlap (GCDIST as well as GCDO) for $m=11$ and $D=3$              | 62       |

| 6.12       | Evaluation of the terms in the stages of a circular digit-serial multiplier with a distributed overlap (GCDIST) for $m=13$ and                                    |          |

|            | D=3                                                                                                                                                               | 63       |

| 6.13 | Evaluation of the terms in the stages of an optimized circular digit-serial multiplier with a distributed overlap (GCDO) for $m = 13$ and $D = 3$                                                         | 63  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

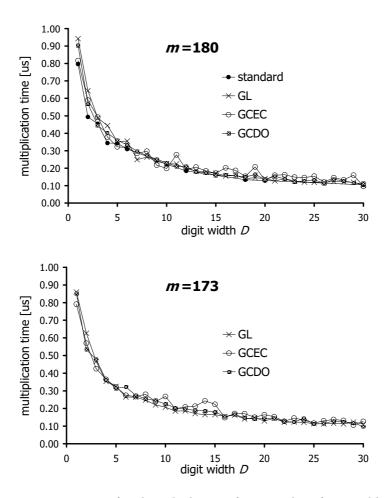

| 6.14 | Time spent for the calculation of one product for variable digit widths                                                                                                                                   | 67  |

| 6.15 | Quality factor as a function of the digit width                                                                                                                                                           | 68  |

| 6.16 | Combinational logic synthesized in the stage of the end-correction multiplier                                                                                                                             | 69  |

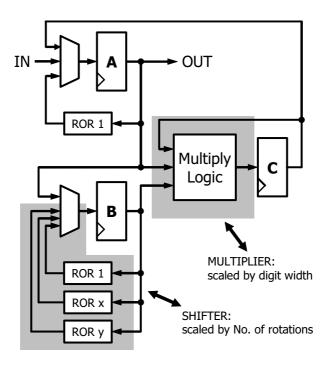

| 7.1  | Arithmetic unit contains 2 scalable subunits, the multiplier and the shifter                                                                                                                              | 74  |

| 7.2  | Approach overview                                                                                                                                                                                         | 76  |

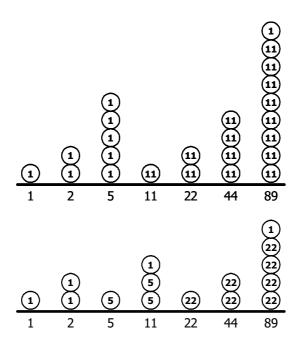

| 7.3  | Heaps of coins for a) 2 nominal values and b) 3 nominal values of coins and for $m=180.$                                                                                                                  | 80  |

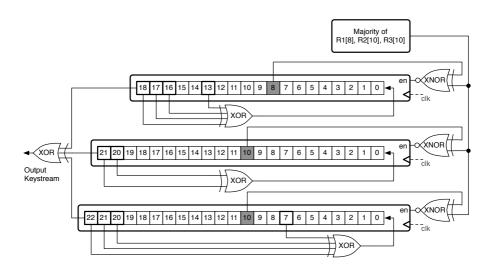

| 10.1 | A5/1 cipher                                                                                                                                                                                               | 90  |

| 10.2 | Algorithm of A5/1                                                                                                                                                                                         | 91  |

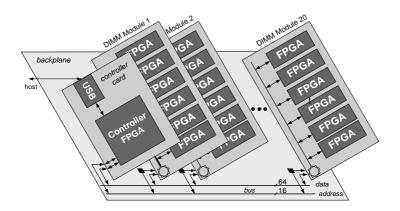

| 10.3 | Architecture of COPACOBANA                                                                                                                                                                                | 98  |

| 10.4 | Photo of COPACOBANA                                                                                                                                                                                       | 98  |

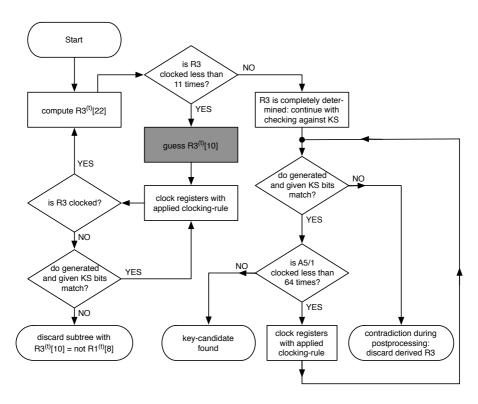

| 11.1 | Flowchart of the FSM of a guessing-engine                                                                                                                                                                 | 103 |

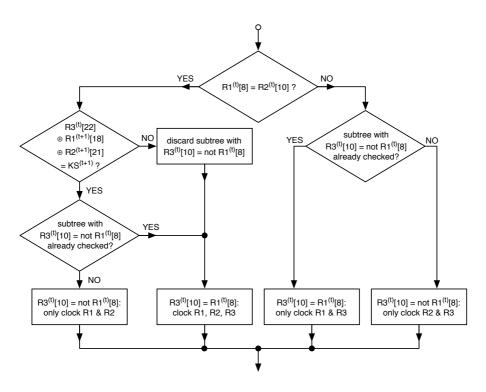

| 11.2 | Guessing the clocking bit of $R3$ in detail                                                                                                                                                               | 104 |

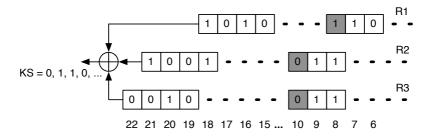

| 11.3 | An example for a generated state candidate after 3 times guessing $R3^{(t)}[10]$                                                                                                                          | 104 |

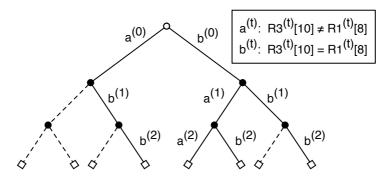

| 11.4 | An example for a reduced binary decision tree of $R3^{(t)}[10]$                                                                                                                                           | 105 |

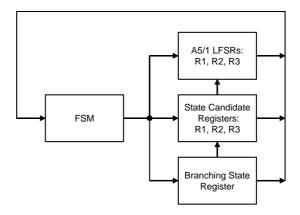

| 11.5 | An overview of the guessing-engine                                                                                                                                                                        | 108 |

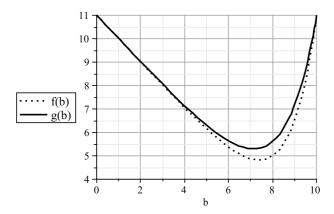

| 11.6 | Functions $f(b), g(b)$ : The average number of cycles clocking $R3$ to generate a state candidate with reloading intermediate states at recovery position $b \dots \dots \dots \dots \dots \dots \dots$ . | 110 |

| 12.1 | One chain in the Hellman TMTO                                                                                                                                                                             | 117 |

| 12.2 | Time-memory trade-off table $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$                                                                                                                                | 118 |

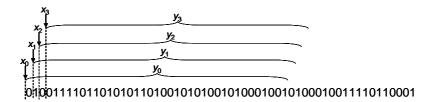

| 12.3 | Sampling the keystream into D output prefixes                                                                                                                                                             | 127 |

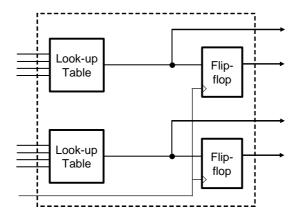

| 13.1  | Simplified diagram of Xilinx FPGA slice                                                                                                                                 | 137 |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| 13.2  | TMTO element — a processing unit calculating one chain of the table                                                                                                     | 138 |  |  |  |  |

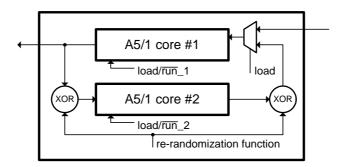

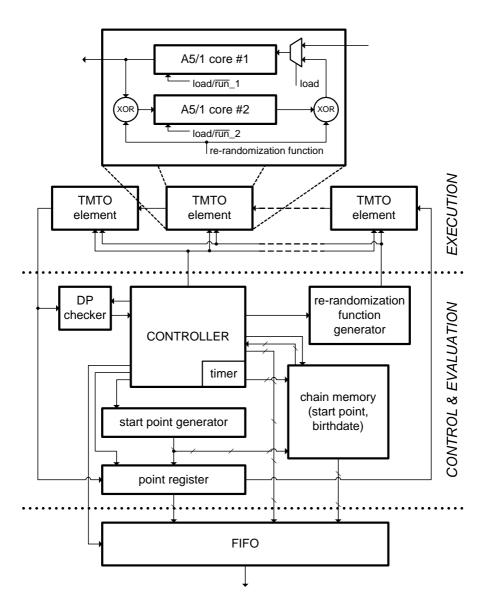

| 13.3  | Architecture of an A5/1 precomputation engine                                                                                                                           | 140 |  |  |  |  |

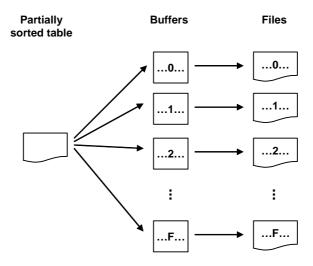

| 13.4  | Memory buffers minimize the fragmentation of files in RadixSort 145                                                                                                     |     |  |  |  |  |

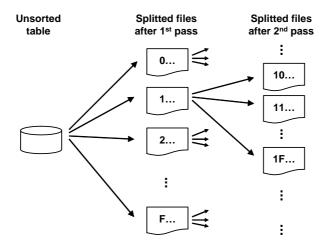

| 13.5  | Splitting an unsorted table into files according to the MSDs of the key                                                                                                 | 147 |  |  |  |  |

| 13.6  | The average length of the chain after the rejection of the duplicate end points                                                                                         | 151 |  |  |  |  |

| 13.7  | The ratio between the number of chains after rejection of the duplicate end points, and the number of generated chains                                                  | 153 |  |  |  |  |

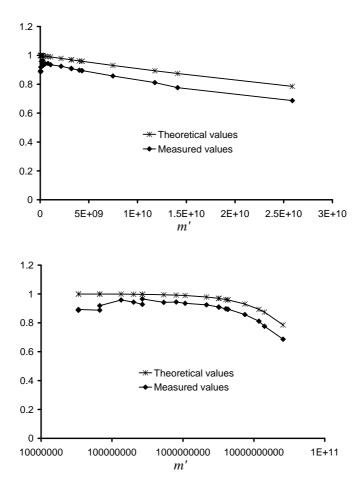

| 13.8  | Both internal state $x_a$ and internal state $x_b$ have the same successor — internal state $x_c$ . Both $x_a$ and $x_b$ produce the same output keystream, $y_a = y_b$ | 154 |  |  |  |  |

| 13.9  | Architecture of the online TMTO element                                                                                                                                 | 156 |  |  |  |  |

| 13.10 | OArchitecture of an A5/1 online engine                                                                                                                                  | 157 |  |  |  |  |

| 13.11 | The TMDTO table is divided into sectors. Border points are stored in a separate table                                                                                   | 161 |  |  |  |  |

| 14.1  | Sequence of internal states in A5/1                                                                                                                                     | 166 |  |  |  |  |

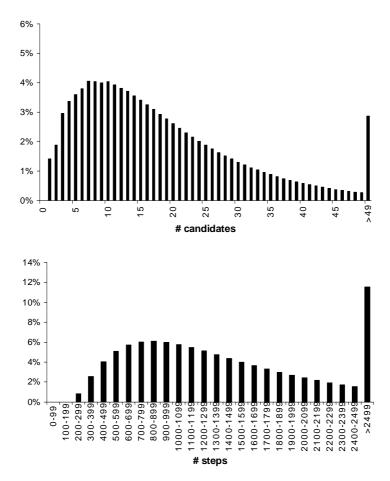

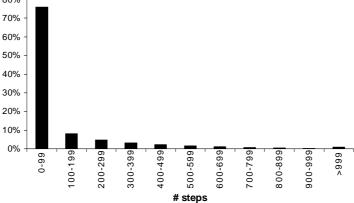

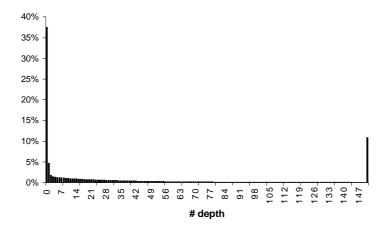

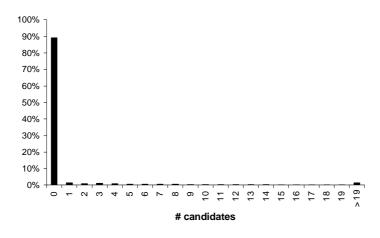

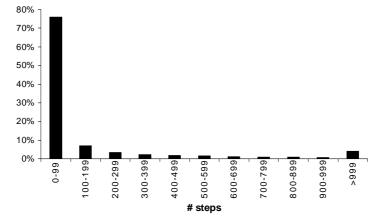

| 14.2  | Test 1: a) Histogram of the candidates for the state $x_i$ , b) Histogram of the number of steps to seek the whole search tree                                          | 174 |  |  |  |  |

| 14.3  | Test 2: a) Histogram of the candidates for the state $x_i$ , b) Histogram of the number of steps to seek the whole search tree                                          | 175 |  |  |  |  |

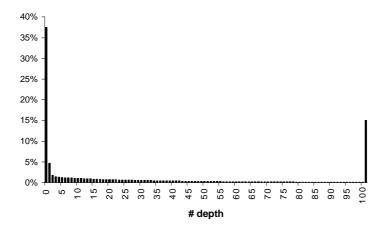

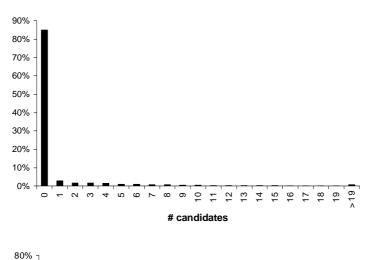

| 14.4  | Test 3: Histogram of the maximum depth reached in the search tree                                                                                                       | 176 |  |  |  |  |

| 14.5  | Test 3: a) Histogram of the candidates for the state $x_i$ , b) Histogram of the number of steps to seek the whole search tree                                          | 177 |  |  |  |  |

| 14.6  | Test 4: Histogram of the maximum depth reached in the search tree                                                                                                       | 178 |  |  |  |  |

| 14.7  | Test 4: a) Histogram of the candidates for the state $x_i$ , b) Histogram of the number of steps to seek the whole search tree                                          | 179 |  |  |  |  |

## Chapter 1

## Introduction

Cryptography increasingly finds its application area in everyday life. Bank transfers, identification cards, admittance systems, communication, the Internet, personal data, databases, they all need to be protected against unauthorized access.

Cryptanalysis, as a complementary discipline to cryptography, is in public view connected with breaking the ciphers for espionage purposes, money thefts, private data surveys etc. However, it is not necessarily that. If done seriously and if all results are published, then the cryptanalysis significantly contributes to cryptography by showing the weaknesses of cryptographic primitives or protocols used in cryptography. Such weaknesses can be then improved, e.g. by replacing the cipher with the stronger one.

Both cryptography and cryptanalysis demand for efficient hardware modules. For example, the cryptographic modules are necessary in RFID tags, used in transportation, in supermarkets, etc. The tag is powered from the electromagnetic field provided by the reader. The communication between the tag and the reader should be accomplished in a reasonable time. Therefore, the cryptographic hardware inside the tag must be cheap, fast, energy-efficient, and providing sufficient cryptographic strength at the same time.

Efficient hardware modules are necessary also in cryptanalysis. For example, when mounting an attack against certain cipher, we are typically given the limited budget and/or the limited hardware resources. Efficient implementation of the hardware modules allows for faster attack and, consequently, better cost-performance ratio.

In this thesis we contribute to both cryptography and cryptanalysis. From each field we have chosen one specific topic. In the first part of the thesis we focus on hardware architectures operating over elements of binary finite fields with normal basis representation. Such architectures are applicable e.g. in Elliptic Curve Cryptography, which increasingly finds its application area e.g. in bank cards, as a replacement of the RSA cipher. We propose the new structure of the normal basis arithmetic unit, which is both small and scalable. The scalability option allows the designer to meet the design constraints optimally.

In the second part of the thesis we focus on cryptanalysis of A5/1 cipher used in GSM communication. We describe hardware architectures of our two attacks on A5/1 cipher. The attacks have been implemented for a special-purpose hardware COPACOBANA. The attacks are designed to utilize both the properties of the cipher and the properties of the programmable devices used in COPACOBANA. Presented design approaches can be reused when designing attacks against similar (stream) ciphers.

### Part I

# Design Methods for Scalable Arithmetic Units over Binary Fields with Normal Basis

## Chapter 2

## Introduction to Part I

History of cryptography is old. In antiquity, middle ages, or in 20th century, there always were messages that had to be encrypted. However, with growing development of information technology in past few decades, the importance of cryptographic systems has increased. Bank transfers, identification cards, admittance systems, communication, the Internet, personal data, databases, they all need to be protected against unauthorized access.

While symmetric cryptosystems use the same key for both encryption and decryption, the asymmetric cryptosystems, based on the idea of Diffie and Hellman [DH76], use two keys. One key — public key — is used for encryption, while the other key — private key — is used for decryption. A nice idea of decrypting messages only with the knowledge of secret private key is replaced with the necessity of higher computational complexity of asymmetric cryptosystems in comparison to the symmetric ones. Therefore, many cryptographic systems, namely those used for transfering large amounts of data, combine advantages of both classes of ciphers. Before the data transfer starts, the key of a symmetric cipher is exchanged by both sides. For this key exchange, the asymmetric cryptosystem is used. Then the data is transferred using the symmetric cipher. Asymmetric cryptosystems are also used in cases where the initial dialog between both sides is impossible (e.g. for the encryption of e-mail messages), or for the authentication — digital signature schemes [FIP00], [ANS97], [ANS98a], [ANS98b] or smart cards [Mas97] can be mentioned here as typical examples.

The RSA cipher [RSA78] is probably the most frequently used asymmetric cipher in currently used applications. Its algorithm is based on a factorization problem. Other algorithms are based either on a discrete logarithm problem (DLP) [DH76] or an elliptic curve discrete logarithm problem (ECDLP) [Mil86], [Kob87].

The elliptic curve cryptosystems (ECC) need significantly shorter keys to achieve the same cryptographic strength as the classical RSA; e.g. the 160-bit ECC has the same cryptographic strength as the 1024-bit RSA [Cer97]. This fact is very important in applications such as smart cards, where the size of hardware or energy consumption is crucial. For this advantage, the EC cryptosystems are commercially more and more popular.

Elliptic curves used for cryptographic purposes have point coordinates which are elements of finite fields, GF(q). Generally, finite fields are defined by a characteristic p and a degree m, marked  $GF(p^m)$ , where the characteristic p is a prime number and the degree m is an integer. In elliptic curve cryptography particularly prime fields GF(p) and binary fields  $GF(2^m)$  are used for a simpler implementation of arithmetic operations. Brief taxonomy may be found e.g. in [Paa99].

In our work we focused on binary fields,  $GF(2^m)$ . Field elements in binary fields are represented either in a polynomial basis or in a normal basis. The choice of the basis has a strong impact on hardware, each of them offering different advantages. Arithmetic units operating over the normal basis require smaller amount of hardware resources [A.1] in comparison to the units operating over the polynomial basis. On the other hand, arithmetic units operating over the polynomial basis are more common, more flexible and they better integrate with integer arithmetics in comparison to the units operating over normal basis. The main goal of this part of the thesis was a development of hardware architectures operating over the normal basis that would be as flexible as those operating over the polynomial basis.

Some applications require the cryptographic system to be as fast as possible, in other applications area and/or power consumption are strongly limited, in yet another applications the data throughput should be "the right one", while the minimum area and energy consumption are desirable. To meet different design constraints the designer has to choose different area/throughput trade-offs. The flexibility of the system in this sense is called *scalability*. The scalability is the crucial characteristics of current cryptographic systems.

The designer expects e.g. no more than a twofold increase in area for a twofold increase in throughput. This is the ideal case. To measure real systems in this aspect we use *quality factor* as the ratio of throughput to area. Although this is not the only possibility, it is the most common measure.

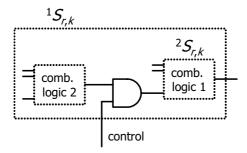

In this part of the thesis we describe a normal basis cryptographic arithmetic unit that we developed. This arithmetic unit is able to perform two crucial operations, multiplication and inversion in normal basis. This unit has been designed to be as small as possible; in fact, it is slightly bigger than the multiplier itself. The arithmetic unit contains two principal subunits, a multiplier and a shifter used in an inversion algorithm. Both subunits may be scaled as much as the designer needs. This extended scalability allows the designer to tune the cryptographic system to fit the design constraints optimally.

This part of the thesis is structured as follows: In Chapter 3, we summarize basic mathematical backgrounds necessary for elliptic curve cryptography. In Chapter 4, we bring an overview on essential algorithms and arithmetic architectures for binary finite fields. In Chapter 5, we describe the multiplication/inversion unit that we developed. As mentioned above, the unit consists of two subunits, the multiplier and the shifter. As the scalability options of a standard multiplier are limited, we developed four architectures of multipliers that can be scaled as much as necessary. These architectures are described in Chapter 6. In the last Chapter 7, we discuss the shifter and its scalability options.

## Chapter 3

## Mathematical Background

In this chapter we summarize mathematical foundations of an elliptic curve cryptography. We remind the definition of an elliptic curve, element operations over elliptic curves and elliptic curves with point coordinates as the elements of finite fields, namely binary fields. The information given here was acquired from annex A of IEEE1363 standard [IEE00] and other sources, e.g.  $[MBG^+93]$ .

#### 3.1 Elliptic Curves

Elliptic curve E over real numbers is a set of points satisfying the Weierstrass equation

$$y^2 = x^3 + ax + b, (3.1)$$

along with an additional element called the *point at infinity* (denoted  $\bigcirc$ ).

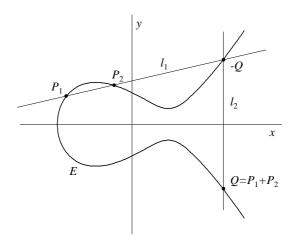

A basic operation defined on an elliptic curve is a point addition. Its geometrical construction is outlined in Figure 3.1.

**Definition 3.1** (Point addition — geometrical approach). Let  $P_1$  and  $P_2$  be two points of elliptic curve E,  $P_1, P_2 \in E$ , with coordinates  $P_1 = [x_1, y_1]$  and  $P_2 = [x_2, y_2]$ . Let  $l_1$  be a secant of E that intersects E at points  $P_1$  and  $P_2$ . Then  $l_1$  intersects E at a third point  $-Q = [x_Q, -y_Q]$ . Point  $Q = [x_Q, y_Q]$  is a result of point addition,  $Q = P_1 + P_2$ .

Point  $-Q = [x_Q, -y_Q]$  is the inverse of point  $Q = [x_Q, y_Q]$ .

Figure 3.1: Point addition on an elliptic curve

**Definition 3.2** (Point doubling — geometrical approach). Let  $P_1 = P_2 = P$  be a point of an elliptic curve E,  $P \in E$ . Let  $l_1$  be a tangent of E that intersects E at a point P. Then  $l_1$  intersects E at a point  $-Q = [x_Q, -y_Q]$ . Point  $Q = [x_Q, y_Q]$  is a result of a point doubling, Q = 2P.

The point at infinity  $\bigcirc$  plays the role of a neutral element:

$$P + \bigcirc = P,$$

$$P + (-P) = \bigcirc.$$

**Definition 3.3** (Point addition — algebraic approach). Let  $P_1$  and  $P_2$  be two points of an elliptic curve E,  $P_1, P_2 \in E$ , with coordinates  $P_1 = [x_1, y_1]$  and  $P_2 = [x_2, y_2]$ . Then the result of addition of points  $P_1$  and  $P_2$  is a point  $Q = P_1 + P_2$  with coordinates  $x_Q, y_Q$ :

$$x_Q = \lambda^2 - x_1 - x_2$$

$y_Q = \lambda(x_1 - x_Q) - y_1$ ,

where

$$\lambda = \frac{y_2 - y_1}{x_2 - x_1}.$$

**Definition 3.4** (Point doubling - algebraic approach). Let  $P_1 = P_2 = P$  be a point of an elliptic curve  $E, P \in E$ , with coordinates  $P = [x_1, y_1]$ . Then the

result of the doubling of a point P is a point Q = 2P = P + P with coordinates  $x_Q, y_Q$ :

$$x_Q = \lambda^2 - 2x_1$$

$$y_Q = \lambda(x_1 - x_Q) - y_1,$$

where

$$\lambda = \frac{3x_1^2 + a}{2y_1}.$$

# 3.2 Elliptic Curves over Binary Finite Fields, $GF(2^m)$

For cryptographic purposes, the coordinates x and y of the points on an elliptic curve are expressed as elements of a finite field GF(q). Generally, the finite field GF(q) has  $q = p^m$  elements, marked  $GF(p^m)$ . Characteristic p is a prime number, the degree m is a positive integer number. In cryptography, particularly prime fields GF(p) and binary fields  $GF(2^m)$  are used for simpler implementation of arithmetic operations.

We focused on elliptic curves over binary fields  $GF(2^m)$ , where field elements can be expressed as m-bit vectors. For the binary fields  $GF(2^m)$ , the Weierstrass equation is

$$y^2 + xy = x^3 + ax^2 + b, (3.2)$$

where a and b are elements of  $GF(2^m)$  with  $b \neq 0$ .

Also the point addition and point doubling are redefined for the elliptic curves over binary fields.

**Definition 3.5** (Point addition on the elliptic curve over the binary field). Let  $P_1$  and  $P_2$  be two points of a elliptic curve E,  $P_1, P_2 \in E$ , with coordinates  $P_1 = [x_1, y_1]$  and  $P_2 = [x_2, y_2]$ ;  $x_1, x_2, y_1, y_2 \in GF(2^m)$ . Then the result of the addition of points  $P_1$  and  $P_2$  is a point  $Q = P_1 + P_2$  with coordinates  $x_Q, y_Q \in GF(2^m)$ :

$$x_Q = a + \lambda^2 + \lambda + x_1 + x_2 \tag{3.3}$$

$$y_Q = \lambda(x_2 + x_Q) + x_Q + y_2, \tag{3.4}$$

where

$$\lambda = \frac{y_2 + y_1}{x_2 + x_1}. (3.5)$$

**Definition 3.6** (Point doubling on the elliptic curve over the binary field). Let  $P_1 = P_2 = P$  be a point of the elliptic curve  $E, P \in E$ , with coordinates  $P = [x_1, y_1]; x_1, y_1 \in GF(2^m)$ . Then the result of the doubling of a point P is a point Q = 2P = P + P with coordinates  $x_Q, y_Q \in GF(2^m)$ :

$$x_O = a + \lambda^2 + \lambda \tag{3.6}$$

$$y_Q = \lambda(x_1 + x_Q) + x_Q + y_1,$$

(3.7)

where

$$\lambda = x_1 + \frac{y_1}{x_1}.\tag{3.8}$$

With the knowledge of the point addition we can define derivative operation — scalar point multiplication.

**Definition 3.7** (Scalar multiplication of the point). Let k be a positive integer  $(k \in \mathbb{N})$  and P be a point on an elliptic curve E,  $P \in E$ . Then a scalar multiple Q = kP is a result of adding k copies of P, Q = kP = P + P + ... + P.

The definition of a scalar point multiplication can be extended to k being zero or k being a negative integer:  $0P = \bigcirc, (-k)P = k(-P)$ .

Scalar point multiplication is the main operation used in elliptic curve cryptography, in other words, it is used in cryptographic primitives. The EC based cryptography utilizes the fact that for given  $k \in \mathbb{N}$  and  $P \in E$  it is relatively simple to compute Q = kP (it takes  $O(\log k)$  point additions or doublings), while the reverse operation — computation of k for known P and Q — is difficult (it takes k-1 point additions). For the evaluation of the scalar point multiple, the double-and-add method (Horner scheme), the addition-subtraction method outlined in [IEE00] or other methods [LD99], [Mon87] can be used.

**Example 3.1.** For  $k = 41 = 11001_2$ , with the double-and-add method the scalar point multiple Q is evaluated after 5 point doublings and 2 point additions:

$$\begin{split} Q &= k \times P = 41 \times P = 101001_2 \times P \\ &= ((((((1P) \times 2 + 0P) \times 2 + 1P) \times 2 + 0P) \times 2 + 0P) \times 2 + 1P). \end{split}$$

Vice versa, to evaluate k from known points P and Q, we must perform 40 point additions  $P+P+P+\ldots+P$  until the result matches the point Q. After that we know the secret value k=41.

The value k is called an *elliptic curve discrete logarithm* (more precise definition of an elliptic curve discrete logarithm is given e.g. in [IEE00]). The problem with evaluation of k for known P and Q is called an *elliptic curve discrete logarithm problem* (ECDLP).

# 3.3 Operations on Binary Field, $GF(2^m)$

From Equations 3.3 through 3.8 it is evident that the following operations on the elements of  $GF(2^m)$  must be implemented:

- addition

- multiplication

- division/inversion

- squaring

If an algorithm for division is not known, then division is performed as multiplication by an inverse element of a divisor (denominator). In that case, an algorithm for inversion is involved. Although squaring is in general derived from multiplication, it is advantageous to consider it as a separate operation, since squaring may be performed faster than multiplication.

Let us remark that in the previous text we operated with so called *affine* coordinates of the points on an elliptic curve. If so called *projective coordinates* are used, than for point addition or point doubling, no division or inversion is necessary. On the other hand, an increased number of multiplications is inevitable. Division, however, is still necessary for conversion from projective to affine coordinates.

Addition of two elements of  $GF(2^m)$  is always realized as a bit-wise addition modulo 2 (XOR operation). The realization of other operations depends on a basis representation of the field elements. There are two common families of basis representations for the binary fields: polynomial basis representations and normal basis representations.

A polynomial basis is a set of the form  $B = \{t^{m-1}, \dots, t^2, t^1, t^0\}$ . The representation of  $GF(2^m)$  via the polynomial basis is carried out by interpreting the bit string  $(a_{m-1} \dots a_2 a_1 a_0)$  as an element  $a_{m-1} t^{m-1} + \dots + a_2 t^2 + a_1 t + a_0$ .

A normal basis is a set of the form  $B = \{\beta^{2^0}, \beta^{2^1}, \beta^{2^2}, \dots, \beta^{2^{m-1}}\}$ . The representation of  $GF(2^m)$  via the normal basis is carried out by interpreting the bit string  $(a_0a_1a_2\dots a_{m-1})$  as the element  $a_0\beta+a_1\beta^2+a_2\beta^4+\dots+a_{m-1}\beta^{2^{m-1}}$ . For more information about normal bases, see [Gao93] and [MBG<sup>+</sup>93].

As arithmetic units working over a normal basis representation are smaller and faster than those ones working over a polynomial basis [A.1], we focused entirely on a normal basis in our work.

# 3.4 Operations on $GF(2^m)$ with a Normal Basis Representation

In our work we entirely focused on a normal basis representation. Here we present algorithms concerning operations in a normal basis mentioned above.

Let

$$B = \{\beta^{2^0}, \beta^{2^1}, \beta^{2^2}, \dots, \beta^{2^{m-1}}\}\$$

be a normal basis in  $GF(2^m)$ . Let a, b be elements of  $GF(2^m)$  with a normal basis B, then

$$a = a_0 \beta^{2^0} + a_1 \beta^{2^1} + a_2 \beta^{2^2} + \dots + a_{m-1} \beta^{2^{m-1}}$$

$$b = b_0 \beta^{2^0} + b_1 \beta^{2^1} + b_2 \beta^{2^2} + \dots + b_{m-1} \beta^{2^{m-1}},$$

where  $a_i, b_i \in GF(2)$ .

### 3.4.1 Addition

Addition of elements a and b is performed as addition of polynomials  $a(\beta)$  and  $b(\beta)$ . As elements of  $GF(2^m)$  are usually represented as m-bit vectors, the addition is equivalent to a bit-wise XOR operation on the vectors a and b.

### 3.4.2 Multiplication

Multiplication of two elements in  $GF(2^m)$  with a normal basis B can be defined by a multiplication matrix M. The multiplication matrix is a square matrix with elements  $\lambda_{j,l} \in GF(2)$ . The algorithm of finding the multiplication matrix M for a given normal basis can be found in [IEE00].

The coefficients of a product  $c = a \times b$  are

$$c_{i} = \sum_{j=0}^{m-1} \sum_{l=0}^{m-1} a_{j+l} b_{l+i} \lambda_{jl}, \ 0 \le i \le m-1,$$

(3.9)

where additions and multiplications are performed in GF(2). Consequently, additions are performed as XOR operations and multiplications as AND operations. The indices of a and b are added modulo m.

Equation 3.9 can be rewritten into following forms:

$$c_i = \sum_{j=0}^{m-1} a_{j+l} \sum_{l=0}^{m-1} b_{l+i} \lambda_{jl}, \ 0 \le i \le m-1,$$

(3.10)

or

$$c_i = \sum_{l=0}^{m-1} b_{l+i} \sum_{j=0}^{m-1} a_{j+l} \lambda_{jl}, \ 0 \le i \le m-1.$$

Let  $C_N$  denotes the number of non-zero elements  $\lambda_{jl}$  in M. As obvious, it corresponds to the number of product terms in Equation 3.9 for each  $c_i$ . Thus,  $C_N$  determines the complexity of multiplication — the higher the number  $C_N$  is, the more complex the multiplication is, i.e. multiplication consumes more time, more area or both. Mullin et al. [MOVW89] proved that the complexity  $C_N \geq 2m-1$ . Bases reaching  $C_N = 2m-1$  are called optimal normal bases. Optimal normal bases belong to the subset of normal bases called Gaussian normal bases. In Gaussian normal bases, the complexity of the base is expressed by the type of a base T. Optimal normal bases are of Type I and Type II. As an illustrative example, let us show a set of equations for m=6 and an optimal normal basis of Type II:

**Example 3.2.** For  $GF(2^6)$  and its optimal normal basis the multiplication matrix  $\mathbf{M}$  is

$$\mathbf{M} = \begin{pmatrix} 0 & 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 \\ 0 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 1 \end{pmatrix}$$

(3.11)

#### **Algorithm 3.1** Normal basis multiplication

```

Input: The multiplication matrix \mathbf{M} for the field GF(2^m); field elements a = (a_0a_1 \dots a_{m-1}) and b = (b_0b_1 \dots b_{m-1}).

Output: The product c = (c_0c_1 \dots c_{m-1}) of a and b.

1: x \leftarrow a

2: y \leftarrow b

3: for k = 0 to m - 1 do

4: (compute via matrix multiplication)

c_k \leftarrow x\mathbf{M}y^{tr}

(where y^{tr} denotes the matrix transpose of the vector y)

5: x \leftarrow LeftShift(x), y \leftarrow LeftShift(y),

(where LeftShift denotes the circular left shift operation)

6: end for

7: return c = (c_0c_1 \dots c_{m-1})

```

Let  $a=(a_0a_1a_2a_3a_4a_5)$  and  $b=(b_0b_1b_2b_3b_4b_5)$  be two elements of  $GF(2^6)$ . After application of a multiplication matrix 3.11 into 3.10 we obtain a following set of equations for bits  $(c_0c_1c_2c_3c_4c_5)$  of result  $c=a\times b$ :

$$c_{0} = a_{0}b_{1} + a_{1}(b_{0} + b_{4}) + a_{2}(b_{3} + b_{4}) + a_{3}(b_{2} + b_{5}) + a_{4}(b_{1} + b_{2}) + a_{5}(b_{3} + b_{5})$$

$$c_{1} = a_{1}b_{2} + a_{2}(b_{1} + b_{5}) + a_{3}(b_{4} + b_{5}) + a_{4}(b_{3} + b_{0}) + a_{5}(b_{2} + b_{3}) + a_{0}(b_{4} + b_{0})$$

$$c_{2} = a_{2}b_{3} + a_{3}(b_{2} + b_{0}) + a_{4}(b_{5} + b_{0}) + a_{5}(b_{4} + b_{1}) + a_{0}(b_{3} + b_{4}) + a_{1}(b_{5} + b_{1})$$

$$c_{3} = a_{3}b_{4} + a_{4}(b_{3} + b_{1}) + a_{5}(b_{0} + b_{1}) + a_{0}(b_{5} + b_{2}) + a_{1}(b_{4} + b_{5}) + a_{2}(b_{0} + b_{2})$$

$$c_{4} = a_{4}b_{5} + a_{5}(b_{4} + b_{2}) + a_{0}(b_{1} + b_{2}) + a_{1}(b_{0} + b_{3}) + a_{2}(b_{5} + b_{0}) + a_{3}(b_{1} + b_{3})$$

$$c_{5} = a_{5}b_{0} + a_{0}(b_{5} + b_{3}) + a_{1}(b_{2} + b_{3}) + a_{2}(b_{1} + b_{4}) + a_{3}(b_{0} + b_{1}) + a_{4}(b_{2} + b_{4})$$

$$(3.12)$$

The set of equations is regular. The equation for bit  $c_{i+k}$  can be derived from the equation for  $c_i$  by a k-bit circular left rotation of arguments a and b. Algorithm 3.1 implements the multiplication of two elements of a field  $GF(2^m)$  represented in a normal basis. This algorithm has been taken from [IEE00].

### 3.4.3 Squaring

Squaring in a normal basis is implemented as a circular shift of an argument "one bit to the right"; if  $a = (a_0 a_1 \dots a_{m-2} a_{m-1})$ , then  $a^2 =$

#### **Algorithm 3.2** Itoh-Teechai-Tsujii inversion in $GF(2^m)$

```

Input: A field GF(2^m) and a nonzero field element \beta

Output: The reciprocal \beta^{-1}

1: Let m-1=b_rb_{r-1}\dots b_1b_0 be the binary representation of m-1, where

the most significant bit b_r of m-1 is 1.

2: \eta \leftarrow \beta, k \leftarrow 1

3: for i = r downto 1 do

\mu \leftarrow \eta

for j = k downto 1 do

5:

\mu \leftarrow \mu^2

6:

end for

7:

\eta \leftarrow \mu \eta, k \leftarrow 2k

8:

if b_{i-1} = 1 then

9:

\eta \leftarrow \eta^2 \beta, \ k \leftarrow k+1

10:

end if

11:

12: end for

13: return \eta^2

```

$(a_{m-1}a_0a_1...a_{m-2})$ . As obvious, this operation is in a normal basis very simple — it can be performed in one or zero clock cycles.

### 3.4.4 Division/Inversion

For division or inversion in a polynomial basis, the extended Euclidean algorithm is used. Unfortunately, this algorithm is not applicable in a normal basis. In a normal basis, division is implemented as multiplication by an inverse element of a divisor.

The fastest known inversion algorithm that can be used in  $GF(2^m)$  with a normal basis is the algorithm developed by Itoh, Teechai, and Tsujii [ITT86] outlined in Algorithm 3.2. Note that the algorithm can be generalized for any  $GF(p^m)$ . The algorithm uses repeated multiplication (steps 8 and 10) and squaring (steps 6, 10 and 13). During the execution of an algorithm,  $r = \lfloor \log(m-1) \rfloor$  multiplications are performed in step 8, and w(m-1) - 1 multiplications are performed in step 10, where  $w(\circ)$  denotes the Hamming weight. Total number of multiplications necessary for one inversion is

$$I_M = |\log(m-1)| + w(m-1) - 1. \tag{3.13}$$

The number of iterative squarings performed in step 6 is

$$I_{IS} = (m-1) - w(m-1). (3.14)$$

The number of squarings performed in step 10 is w(m-1)-1, and there is one last squaring in step 13 [ITT86]. A total number of squarings necessary for one inversion is then

$$I_S = m - 1.$$

(3.15)

# Chapter 4

# Previous work

Multiplication is the crucial operation to be implemented over  $GF(2^m)$  with a normal basis. Other operations are in a normal basis either simple or based on multiplication. There has been an array of normal basis multipliers developed. An overview of several architectures of normal basis multipliers can be found e.g. in [ANR99]. Alternative architectures with a slightly reduced gate count or a critical path were reported in [GS00, RMH03, KGKH04]. Some multipliers are optimized for special cases of normal bases, mainly to the optimal normal bases of both Type I [KS98] and Type II [Kwo03, SK01]. Here we deal with Massey-Omura multiplier [MO86] that can be used for any type of a normal basis, and with its pipelined version by Agnew et al. [AMOV91].

# 4.1 Massively Parallel Multiplier

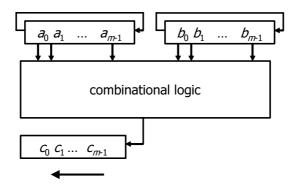

The set of equations defining the bits of result (see example set 3.12) can be implemented as a combinational logic that computes all bits of a result in parallel. Such a multiplier is huge (the amount of hardware is proportional to  $m^2$ , in the best case) and the critical path is long (it is proportional to  $\log m$ ) This multiplier is also called *bit-parallel*.

Figure 4.1: Massey-Omura multiplier

## 4.2 Massey-Omura Multiplier

Massey and Omura [MO86] proposed a multiplier that employs the regularity of equations for all bits of a result. If we construct an equation for one bit of a result (e.g.  $c_0$ ), equations for other bits can be derived by rotating bits of arguments a and b, as shown in Algorithm 3.1 (see also an example set of Equations 3.12). In this multiplier, one bit of the result is computed in one clock cycle and the registers holding arguments a and b are rotated one bit to the left between cycles. The Massey-Omura multiplier is m times smaller than the massively parallel one because it contains logic for the computation of one bit only. The computation of the result takes m clock cycles. The length of the critical path remains the same as for the massively parallel multiplier. This multiplier is also called bit-serial. The block structure of the Massey-Omura multiplier is shown in Figure 4.1.

# 4.3 Pipelined Massey-Omura Multiplier

Agnew, et al. [AMOV91] modified the Massey-Omura multiplier by pipelining and parallelization. From Equation 3.10 it follows, that the equation for each bit of result can be divided into m terms  $T_{i,j}$ :

$$c_i = T_{i,0} + T_{i,1} + \dots + T_{i,m-2} + T_{i,m-1} = \sum_{j=0}^{m-1} T_{i,j},$$

(4.1)

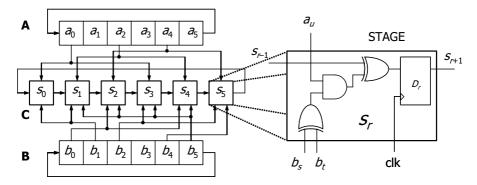

Figure 4.2: Modification of the Massey-Omura multiplier by Agnew et al. Structure shown here is for  $GF(2^6)$  and its optimal normal basis

where

$$T_{i,j} = a_{j+i} \sum_{l=0}^{m-1} b_{l+i} \lambda_{jl}$$

(4.2)

(the values of the subscript indices are reduced modulo m).

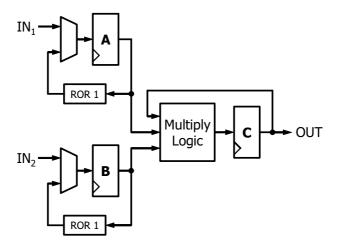

In the multiplier by Agnew et al., the computation of the result is again performed in m clock cycles. In the k-th clock cycle, terms  $T_{i,i+k}$  ( $\forall i, 0 \leq i \leq m-1$ ) are evaluated and added to the intermediate results of the corresponding bits  $c_i$ . Registers A and B that hold arguments a and b are rotated one bit right in every clock cycle. As pipelining is used, also the register C, in which the result is successively evaluated, is rotated one bit right in every clock cycle. The result in the register C is available after m clock cycles. For illustration, the block structure of a multiplier for the set of Equations 3.12 is shown in Figure 4.2. The initial content of registers A and B is shown in this figure.

The combinational logic, which lies in front of each C register bit, implements one term. Denote the logic together with the register bit a *stage*. The amount of hardware in the multiplier by Agnew et al. is the same as for the Massey-Omura multiplier, but the combinational logic is distributed over the stages  $s_0s_1...s_{m-1}$  of the register C. Thus the critical path is short and constant (it does not depend on m) and the maximum achievable frequency is higher.

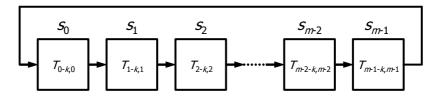

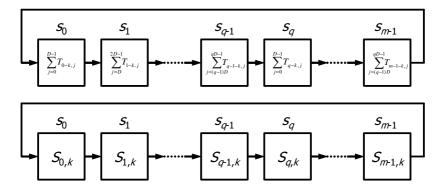

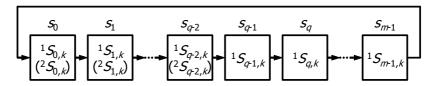

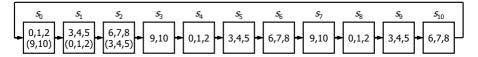

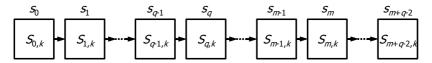

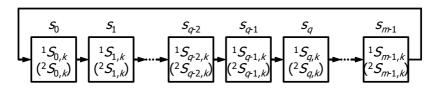

**Rule 4.1** (pipelined Massey-Omura multiplier). Let q=m be the number of clock cycles of one multiplication. Then, in the k-th clock cycle  $(0 \le k \le q-1)$ , the stage  $s_r$   $(0 \le r \le m-1)$  evaluates the term

$$S_{r,k} = T_{r-k,r} \tag{4.3}$$

(the values of the subscript indices are reduced modulo m).

After substituting 4.2 into 4.3 we get

$$S_{r,k} = T_{r-k,r} = a_{r+r-k} \sum_{l=0}^{m-1} b_{l+r-k} \lambda_{rl},$$

$$S_{r,k} = a_{2r-k} \sum_{l=0}^{m-1} b_{(l+r)-k} \lambda_{rl}$$

$$(4.4)$$

(the values of the subscript indices are reduced modulo m).

The term  $S_{r,k}$  is added to the partial result of the bit  $c_{r-k}$ , which is, due to the rotation of the register C, present in the stage  $s_r$  during the k-th clock cycle. The result  $c_0c_1c_2...c_{m-1}$  is available in stages  $s_{m-1}s_0s_1...s_{m-2}$  after m clock cycles.

Let us briefly explain the functionality of the multiplier. From Equations 4.3 and 4.4 follows that in the first clock cycle (k = 0), stage  $s_r$  evaluates the term (see also Figure 4.3)

$$S_{r,0} = T_{r,r}$$

or

$$S_{r,0} = a_{2r-0} \sum_{l=0}^{m-1} b_{(l+r)-0} \lambda_{rl}$$

(4.5)

(the values of the subscript indices are reduced modulo m).

From the comparison of Equations 4.5 and 4.4 is obvious that to evaluate an appropriate term  $S_{r,k}$  in the k-th clock cycle, only arguments a and b are needed to rotate k bits to the right. Arguments a and b are held in registers A and B.

From Equation 4.1 follows that on its run around the register C, the bit  $c_i$  must "collect" all terms  $T_{i,j}$  with an equal first index i and with all distinct second indices  $j, 0 \le j \le m-1$ . The equality of the first index i is satisfied by the rotation of the register C — the term  $T_{r-k,r}$  is added to the partial result

Figure 4.3: Terms evaluated in the stages of the register C in the bit-serial multiplier in the k-th clock cycle

of the bit  $c_{r-k}$  in the stage  $s_r$  during the k-th clock cycle. The second index j is fixed with an appropriate stage  $s_j$  (see 4.3). As every bit  $c_i$  of the result passes all stages  $s_j$ , it "collects" all terms  $T_{i,j}$ .

Let us note that the description given in Rule 4.1 corresponds to the one given at [AMOV91]. In this description, in the first clock cycle (k = 0), the stage  $s_r$  evaluates the term  $T_{r,r}$ . However, it is possible to make permutation of terms  $T_{i,j}$ . Generally, we have to only satisfy that the terms  $T_{i,j}$  concurrently evaluated in stages  $s_0s_1 \ldots s_{m-1}$  during one clock cycle have distinct values of indices i as well as distinct values of indices j.

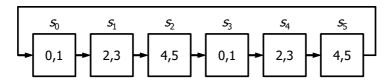

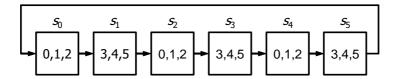

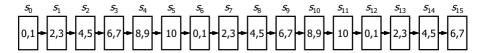

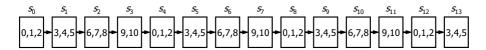

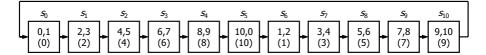

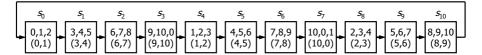

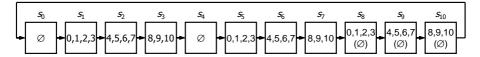

**Example 4.1.** It is shown in Figure 4.4 how the product c from Example 3.2 is successively evaluated in a pipelined bit-serial multiplier. In the first clock cycle (k=0) boxed terms are evaluated, in the second clock cycle (k=1) overlined terms are evaluated etc. Multiplication takes q=m=6 clock cycles.

In the following we will sketch the proof of correctness of the pipelined Massey-Omura multiplier. Outline of the proof will be used for proofs of other multipliers. To prove the correctness of any of the multipliers we have to show that the Equation 4.1 is satisfied for any  $c_i$ .

Proof of correctness of the bit-serial multiplier. Let i = r - k. From Rule 4.1 it follows that in the k-th clock cycle the partial result of the bit  $c_i$  is present in the stage  $s_{i+k}$ . The stage  $s_{i+k}$  evaluates the term  $S_{i+k,k} = T_{i,i+k}$  which is added to the partial result of  $c_i$  present in the stage. As evaluation takes q = m clock cycles, then

$$c_i = \sum_{k=0}^{m-1} S_{i+k,k} = \sum_{k=0}^{m-1} T_{i,i+k}$$

$$c_0 = \boxed{a_0b_1} + \overline{a_1(b_0 + b_4)} + a_2(b_3 + b_4) + a_3(b_2 + b_5) + a_4(b_1 + b_2) + a_5(b_3 + b_5)$$

$$c_1 = a_1b_2 + \boxed{a_2(b_1 + b_5)} + \overline{a_3(b_4 + b_5)} + a_4(b_3 + b_0) + a_5(b_2 + b_3) + a_0(b_4 + b_0)$$

$$c_2 = a_2b_3 + a_3(b_2 + b_0) + \boxed{a_4(b_5 + b_0)} + \overline{a_5(b_4 + b_1)} + a_0(b_3 + b_4) + a_1(b_5 + b_1)$$

$$c_3 = a_3b_4 + a_4(b_3 + b_1) + a_5(b_0 + b_1) + \boxed{a_0(b_5 + b_2)} + \overline{a_1(b_4 + b_5)} + a_2(b_0 + b_2)$$

$$c_4 = a_4b_5 + a_5(b_4 + b_2) + a_0(b_1 + b_2) + a_1(b_0 + b_3) + \boxed{a_2(b_5 + b_0)} + \overline{a_3(b_1 + b_3)}$$

$$c_5 = \overline{a_5b_0} + a_0(b_5 + b_3) + a_1(b_2 + b_3) + a_2(b_1 + b_4) + a_3(b_0 + b_1) + \boxed{a_4(b_2 + b_4)}$$

Figure 4.4: Evaluation of terms in pipelined bit-serial multiplier by Agnew et al. (for  $GF(2^6)$  and its optimal normal basis)

As the indices are reduced modulo m, the Equation 4.1 is satisfied.  $\Box$

### 4.4 Other Multipliers

Reyhani-Masoleh and Hasan [RMH03] proposed two other architectures of the multiplier. By utilizing the symmetric property of the multiplication, their multipliers have reduced area complexity in comparison to the multiplier by Agnew et al. On the other hand, the critical path of these multipliers is slightly longer, or at least comparable to that of the multiplier by Agnew et al.

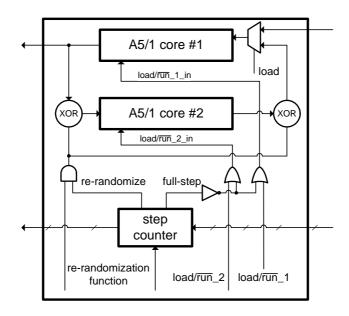

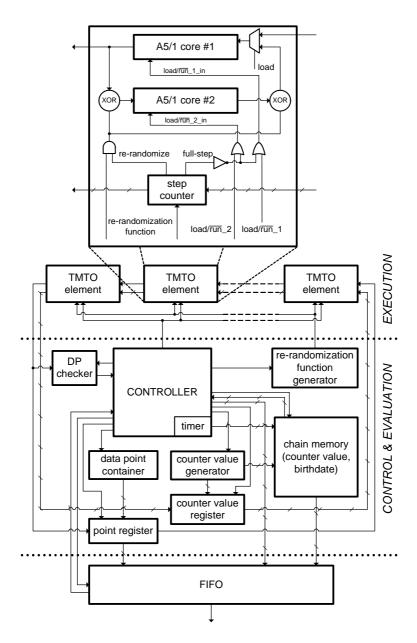

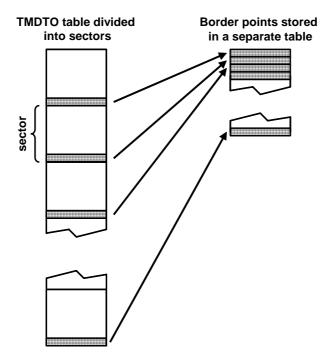

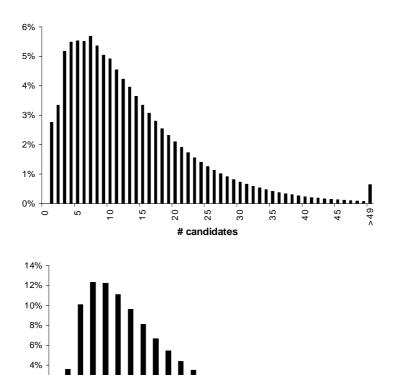

Kwon et al. [KGKH04] proposed another structure for a pipelined bit-serial multiplier. Their multiplier is applicable only for odd values of m. The multiplier has the area complexity comparable to the multiplier by Reyhani-Masoleh and Hasan, while it preserves the critical path delay of the multiplier by Agnew et al.